**Programmer's Reference Series**

# **NOVA<sup>®</sup> Line Computers**

# DataGeneral

**Programmer's Reference Series**

# **NOVA® Line Computers**

Data General Corporation, Westboro, Massachusetts 01581

## NOTICE

Data General Corporation (DGC) has prepared this manual for use by DGC personnel, licensees, and customers. The information contained herein is the property of DGC and shall not be reproduced in whole or in part without DGC's prior written approval.

Users are cautioned that DGC reserves the right to make changes without notice in the specifications and materials contained herein and shall not be responsible for any damages (including consequential) caused by reliance on the materials presented, including, but not limited to typographical, arithmetic, or listing errors.

NOVA, INFOS and ECLIPSE are registered trademarks of Data General Corporation, Westboro, Massachusetts. DASHER and microNOVA are trademarks of Data General Corporation, Westboro, Massachusetts.

#### **FIRST EDITION**

Second Printing, July 1979

First Printing December 1978

Ordering No. 014-000631 ©Data General Corporation, 1978, 1979 All Rights Reserved Printed in the United States of America Rev. 01, July 1979

# TABLE OF CONTENTS

## SECTION I

# NOVA LINE COMPUTERS

Page

| INTRODUCTION                            | I-1 |

|-----------------------------------------|-----|

| Efficient Basic Instruction Set         | I-1 |

| Stack                                   | I-1 |

| Multiply/Divide                         | I-1 |

|                                         | I-2 |

| Memory Allocation and Memory Management | I-2 |

| Memory                                  | I-2 |

| Auto-Increment/Decrement                | I-3 |

|                                         | I-3 |

| Real-Time Clock                         | I-3 |

| Input/Output Bus                        | I-3 |

| Device Addressability                   | I-3 |

| Interrupt Capability                    | I-3 |

| Data Channel                            | I-3 |

| Ease of Interfacing                     | I-4 |

| Input/Output Devices                    | I-4 |

| Software                                | I-4 |

| Languages                               | I-4 |

| Operating Systems                       | [-4 |

| Conclusion                              | I-4 |

## SECTION II

# INTERNAL STRUCTURE

| INTRODUCTION                                 | II-1         |

|----------------------------------------------|--------------|

| INFORMATION FORMATS                          | II-1         |

| Bit Numbering                                | II <b>-1</b> |

| Octal Representation                         | II-2         |

| Character Codes                              |              |

| Information Representation                   |              |

| Integers                                     | II-3         |

| Floating Point                               |              |

| Logical Quantities                           | II-5         |

| Decimal Numbers                              | II-5         |

| INFORMATION ADDRESSING                       |              |

| Word Addressing                              | II-6         |

| Effective Address Calculation                |              |

| Auto-Increment/Decrements                    | II-7         |

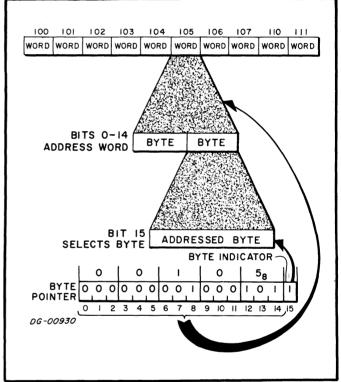

| Byte Addressing                              |              |

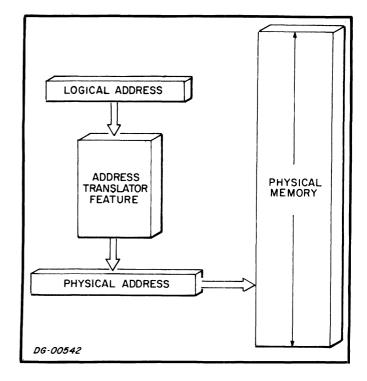

| Addressing With Address Translation Hardware | II-9         |

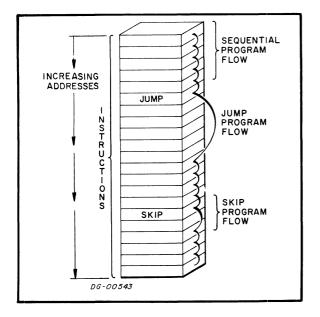

| PROGRAM EXECUTION                            | II-10        |

| Program Flow Alteration                      | II-10        |

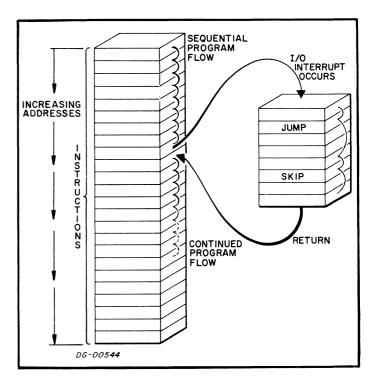

| Program Flow Interruption                    | II-10        |

# SECTION III

## **INSTRUCTION SETS**

|                                                                                                                                                                                                               | Page                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| INTRODUCTION                                                                                                                                                                                                  | III-1                                                                         |

| INSTRUCTION FORMATS                                                                                                                                                                                           | III-1                                                                         |

| CODING AIDS                                                                                                                                                                                                   | III-3                                                                         |

| FIXED POINT ARITHMETIC<br>LOAD ACCUMULATOR<br>STORE ACCUMULATOR<br>ADD<br>SUBTRACT<br>NEGATE<br>ADD COMPLEMENT<br>MOVE.<br>INCREMENT                                                                          | III-5<br>III-5<br>III-5<br>III-5<br>III-5<br>III-5<br>III-5                   |

| LOGICAL OPERATIONS                                                                                                                                                                                            |                                                                               |

| STACK MANIPULATION .<br>Stack Pointer .<br>Frame Pointer .<br>Return Block .<br>Stack Frames .<br>Stack Protection .<br>Initialization of the Stack Control Registers .<br>Stack Pointer .<br>Frame Pointer . | III-8<br>III-8<br>III-8<br>III-9<br>III-9<br>III-9<br>III-9<br>III-9<br>III-9 |

| STACK MANIPULATION INSTRUCTIONS<br>PUSH ACCUMULATOR<br>POP ACCUMULATOR<br>SAVE<br>MOVE TO STACK POINTER<br>MOVE TO FRAME POINTER<br>MOVE FROM STACK POINTER<br>MOVE FROM FRAME POINTER                        | III-10<br>III-10<br>III-10<br>III-10<br>III-10<br>III-10<br>III-10            |

| PROGRAM FLOW ALTERATION<br>JUMP<br>JUMP TO SUBROUTINE.<br>INCREMENT AND SKIP IF ZERO<br>DECREMENT AND SKIP IF ZERO<br>Extended Instructions<br>RETURN<br>TRAP                                                 | III-11<br>III-11<br>III-11<br>III-11<br>III-12<br>III-12                      |

# SECTION IV

# INPUT/OUTPUT

|                                                                                                                  | Page                                 |

|------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| INTRODUCTION                                                                                                     | IV-1                                 |

| OPERATION OF I/O DEVICES                                                                                         | IV-1                                 |

| PRIORITY INTERRUPTS                                                                                              | IV-2                                 |

| DATA CHANNEL                                                                                                     | IV-3                                 |

| CODING AIDS                                                                                                      | IV-3                                 |

| DATA IN A<br>DATA IN B<br>DATA IN C<br>DATA OUT A<br>DATA OUT B<br>DATA OUT C<br>I/O SKIP                        | IV-3<br>IV-3<br>IV-4<br>IV-4<br>IV-4 |

| INTERRUPT ENABLE<br>INTERRUPT DISABLE<br>READ SWITCHES<br>INTERRUPT ACKNOWLEDGE<br>MASK OUT<br>I/O RESET<br>HALT | IV-5<br>IV-5<br>IV-5<br>IV-6<br>IV-6 |

## SECTION V

# **PROCESSOR OPTIONS**

| INTRODUCTION                    | V-1 |

|---------------------------------|-----|

| POWER FAIL                      | V-1 |

| SKIP IF POWER FAIL FLAG IS ONE  | V-1 |

| SKIP IF POWER FAIL FLAG IS ZERO | V-1 |

| MULTIPLY/DIVIDE                 |     |

| NOVA Multiply/Divide            | V-1 |

| Non-NOVA Multiply/Divide        | V-2 |

| MULTIPLY.                       | V-2 |

| DIVIDE                          | V-2 |

| REAL-TIME CLOCK                 |     |

| SELECT RTC FREQUENCY            | V-3 |

# SECTION V (Continued)

# PROCESSOR OPTIONS

|                                                      | Page       |

|------------------------------------------------------|------------|

| MEMORY PARITY OPTION                                 | V-3        |

| Method of Operation                                  |            |

| READ PARITY ERROR ADDRESS                            | V-3.1      |

| READ EXTENDED ERROR ADDRESS                          |            |

| MEMORY MANAGEMENT                                    | V-4        |

| Background to Address Translation                    |            |

| ADDRESS TRANSLATION USING THE NOVA 830 AND 840 MMPU  | <b>V-6</b> |

| LOAD MAP                                             |            |

| LOAD DEVICE PROTECTION                               |            |

| LOAD PROTECTION CONTROL                              |            |

| ENABLE USER MAP                                      | V-7        |

| INITIATE PAGE CHECK                                  |            |

| READ STATUS                                          |            |

| READ INSTRUCTION ADDRESS                             |            |

| READ INVALID ADDRESS                                 |            |

| ENABLE SINGLE CYCLE                                  |            |

| SUPERVISOR CALL                                      | V-9        |

| SUPERVISOR PROGRAMMING FOR THE NOVA 830 AND 840 MMPU | V-10       |

| Setting Up For Translation                           |            |

| MMPU Protection Processing                           |            |

| I/O Protection                                       |            |

| Validity Protection                                  |            |

| Runaway Defer Protection                             |            |

| Write Protection                                     |            |

| Device Interrupt Processing                          |            |

|                                                      | 17 10      |

| ADDRESS TRANSLATION USING THE MMU                    |            |

| LOAD MAP                                             | V-12       |

| INITIATE PAGE CHECK PAGE CHECK                       | V-13       |

|                                                      |            |

| READ MMU STATUS                                      |            |

| WRITE MMU STATUS                                     |            |

| MAP SINGLE CYCLE                                     | V-14       |

| SUPERVISOR PROGRAMMING FOR THE MMU                   | V-15       |

| Setting Up For Translation                           | V-15       |

| Device Interrupt Processing                          | V-15       |

|                                                      |            |

| ADDRESS TRANSLATION USING THE NOVA 3 MMU AND MPU     |            |

| LOAD MAP                                             |            |

| INITIATE PAGE CHECK                                  |            |

| PAGE CHECK ••••••                                    |            |

| READ MMPU STATUS                                     |            |

| WRITE MMPU STATUS                                    |            |

| READ VIOLATION DATA                                  |            |

| READ VIOLATION ADDRESS                               |            |

| MAP SINGLE CYCLE                                     | V-15.4     |

# SECTION V (Continued)

# PROCESSOR OPTIONS

| CLEAR VIOLATIONCLEAR MAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V-15.4<br>V-15.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUPERVISOR PROGRAMMING FOR THE NOVA 3 MMPU<br>Setting Up for Translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V-15.5<br>V-15.6<br>V-15.6<br>V-15.6<br>V-15.6<br>V-15.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| FLOATING POINT ARITHMETIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| INSTRUCTION SET .<br>LOAD SINGLE .<br>LOAD DOUBLE .<br>STORE SINGLE .<br>STORE SINGLE .<br>ADD SINGLE .<br>ADD DOUBLE .<br>SUBTRACT SINGLE .<br>SUBTRACT DOUBLE .<br>MULTIPLY SINGLE .<br>DIVIDE SINGLE .<br>DIVIDE SINGLE .<br>DIVIDE DOUBLE .<br>Temporary Buffer Instructions .<br>MOVE FPAC TO TEMP .<br>MOVE TEMP TO FPAC .<br>ADD TEMP TO FPAC (SINGLE) .<br>SUBTRACT TEMP FROM FPAC (SINGLE) .<br>SUBTRACT TEMP FROM FPAC (DOUBLE) .<br>MULTIPLY FPAC BY TEMP (SINGLE) .<br>MULTIPLY FPAC BY TEMP (DOUBLE) .<br>MULTIPLY FPAC BY TEMP (DOUBLE) .<br>DIVIDE FPAC BY | $\begin{array}{c} V-17\\ V-17\\ V-17\\ V-17\\ V-17\\ V-17\\ V-18\\ V-18\\ V-18\\ V-18\\ V-19\\ V-19\\ V-19\\ V-19\\ V-19\\ V-19\\ V-20\\ V-20\\ V-20\\ V-20\\ V-20\\ V-21\\ V-21\\ V-21\\ V-21\\ V-21\\ V-22\\ V-22\\ V-22\\ V-22\\ V-22\\ V-22\\ V-22\\ V-23\\ V-23\\$ |

| ABSOLUTE VALUE<br>CLEAR FPAC<br>LOAD EXPONENT<br>NEGATE<br>NORMALIZE<br>READ HIGH WORD<br>SCALE<br>Status Instructions<br>READ STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V-23<br>V-23<br>V-23<br>V-23<br>V-23<br>V-23<br>V-23<br>V-24<br>V-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# SECTION V (Continued) PROCESSOR OPTIONS

Page

| WRITE STATUS                              | · · · · · · · · · · · · · · · · · · ·  |

|-------------------------------------------|----------------------------------------|

| Diagnostic Instructions                   |                                        |

| READ WORD 1                               | ····· V-2                              |

| READ WORD 2                               | ····· V-2                              |

| READ WORD 3                               | •••••••••••••••••••••••••••••••••••••• |

| READ WORD 4                               | ····· V-2                              |

| FPU CLOCK                                 | ····· V-2                              |

| Mode Settings For The Floating Point Unit |                                        |

| Normal Mode                               | V-2                                    |

| Parallel Mode                             |                                        |

| Interrupt Enable and Disable              |                                        |

| •                                         |                                        |

| FLOATING POINT UNIT MNEMONICS             | ····· V-2                              |

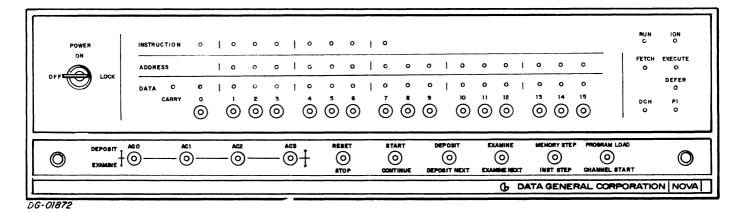

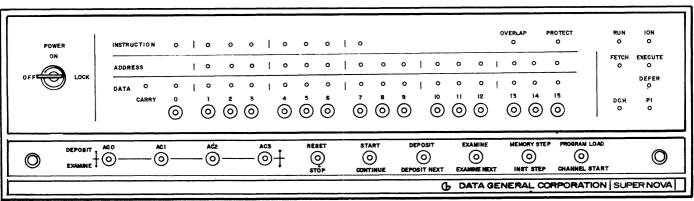

## SECTION VI

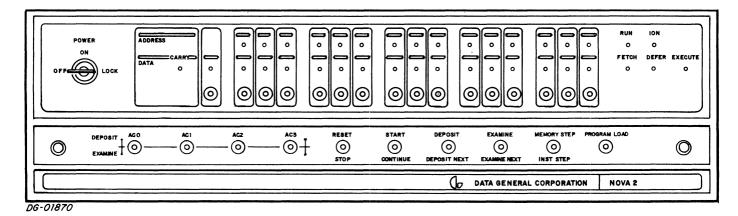

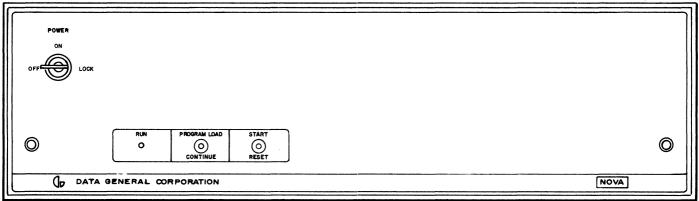

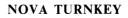

## FRONT PANEL

| INTRODUCTION               | VI-1 |

|----------------------------|------|

| DATA SWITCHES              | VI-4 |

| CONSOLE SWITCHES           | VI-4 |

| Accumulator DepositExamine | VI-4 |

| Reg DepReg Exam            |      |

| ResetStop                  |      |

| StartContinue              |      |

| DepositDeposit Next        | VI-4 |

| ExamineExamine Next        |      |

| Memory StepInst Step       | VI-5 |

| Program Load               |      |

| Channel Start              | VI-5 |

| Power                      | VI-5 |

| PROGRAM LOADING            | VI-6 |

| Manual Loading             |      |

| Automatic Loading          |      |

# APPENDICES

Page

| APPENDIX A<br>I/O DEVICE CODES AND DATA GENERAL MNEMONICS A· | -2 |

|--------------------------------------------------------------|----|

| APPENDIX B<br>OCTAL AND HEXADECIMAL CONVERSION B·            | -1 |

| APPENDIX C<br>ASCII CHARACTER CODES C·                       | -1 |

| APPENDIX D<br>DOUBLE PRECISION ARITHMETIC D-                 | -1 |

| APPENDIX E<br>INSTRUCTION USE EXAMPLES E·                    | -1 |

| APPENDIX F<br>INSTRUCTION EXECUTION TIMES F                  | -1 |

viii

# **SECTION I**

# **NOVA LINE COMPUTERS**

#### INTRODUCTION

The Data General Corporation NOVA line of computers are general purpose, four-accumulator, stored-program computers, with a word length of 16 bits. The maximum amount of main memory is 32,768 16-bit words. For the NOVA 830 and NOVA 840 computers with the MMPU feature, and for the NOVA 3/12 computer with the MMU feature and the NOVA 3/D with the MMU and MPU feature, the maximum amount of main memory is 131,072 16-bit words. The accumulators are also 16 bits in length and are used for arithmetic and logical operations. Furthermore, two of the accumulators can be used as index registers. Memory can be addressed either directly or by using indirect addresses. Chains of indirect addresses can be of any length. A direct memory access (DMA) data channel is provided to enable rapid data transfer between main memory and peripheral devices. The flexible design of the NOVA line of computers allows the convenient implementation of applications in all sectors of the data processing field.

The standard instruction set contains instructions that perform fixed point arithmetic and logical operations between accumulators, transfer of operands between accumulators and main memory, transfer of program control, and input/output (I/O) operations. Options are available that add instructions to this set. These additional instructions perform such operations as multiply/divide, floating point calculations, memory allocation and protection, and memory management and protection.

The NOVA line of computers is made up of the NOVA computer, the SUPERNOVA<sup>®</sup> computer, the NOVA 1200 series, the NOVA 800 series, the NOVA 2 series, and the NOVA 3 series. The NOVA 1200 series consists of the NOVA 1200 computer, the NOVA 1210 computer, the NOVA 1220 computer, and the NOVA 1200 Jumbo computer. The NOVA 800 series consists of the NOVA 800 computer, the NOVA 820 computer, the NOVA 800 Jumbo computer, the NOVA 820 computer, and the NOVA 840 computer. The NOVA 2 series consists of the NOVA 2/4 computer and the NOVA 2/10 computer. The NOVA 3 series consists of the NOVA 3/4 computer, the NOVA 3/12 computer, and the NOVA 3/D computer. While these computers differ in specifics such as processing speed, they all share the same general architecture. This means that, in general, software is compatible across the entire line. To a somewhat lesser degree, hardware is also compatible across the line. The features of the NOVA line are summarized below.

#### **Efficient Basic Instruction Set**

The basic instruction set for the NOVA line of computers contains instructions that perform fixed point arithmetic and logical operations between accumulators, transfer of operands between accumulators and main memory, transfer of program control, and I/O operations. All instructions are one 16-bit word in length. The arithmetic and logical instructions have the capability to perform, in one instruction, the following sequence: perform an operation, shift the result one bit left or right, test the result of the shift, and then conditionally skip the next instruction depending upon the outcome of the test. In addition, it is possible to perform this entire sequence without affecting either of the operands. This means that complicated numerical manipulation and testing can be performed using a small number of instructions.

#### Stack

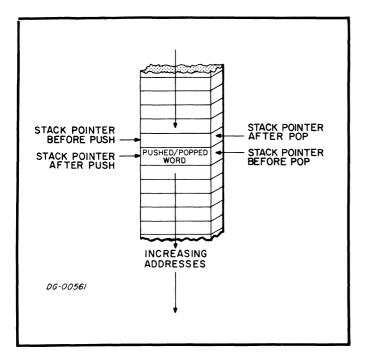

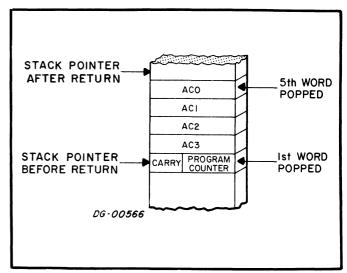

A Last-In/First-Out (LIFO) or push-down stack is maintained by the NOVA 3 processor. This feature provides a convenient method for the saving of return information and passing arguments between subroutines. The stack also provides an expandable area for the temporary storage of variables and intermediate results.

#### Multiply/Divide

The multiply/divide feature allows the multiplication and division of operands to be performed quickly, without resorting to time-consuming software routines. Two 16-bit fixed point operands can be multiplied together to yield a 32-bit fixed point result. A 16-bit fixed point operand can be divided into a 32-bit fixed point operand to yield a 16-bit fixed point quotient and a 16-bit fixed point remainder.

#### **Floating Point**

The floating point feature allows the manipulation of both single precision (32 bits) and double precision (64 bits) floating point numbers. Single precision gives 6-7 significant decimal digits while double precision gives 13-15 significant decimal digits. The decimal range of a floating point number is approximately  $5.4 \times 10-79$  to  $7.2 \times 10+75$  in either precision.

The floating point feature contains two 64-bit floating point accumulators. Floating point calculations can take place between these two accumulators or between one of the accumulators and operands in main memory.

#### **Memory Allocation and Memory Management**

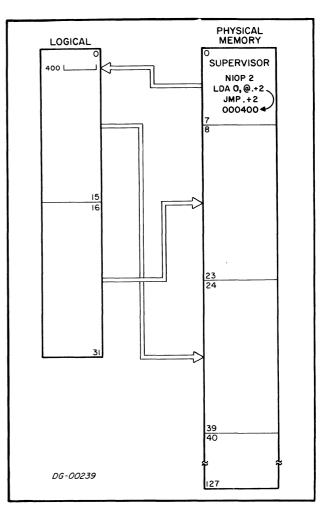

There are three features available with NOVA line computers that perform memory allocation and memory management. All of them perform logicalto-physical address translation, and two of them allow certain protection features to be implemented.

The memory management and protection unit (MMPU) is available with the NOVA 830 computer and the NOVA 840 computer. The memory management unit (MMU) is available with the NOVA 3/12 computer. The NOVA 3 memory management unit (MMU) and memory protection unit (MPU) are available with the NOVA 3/D computer.

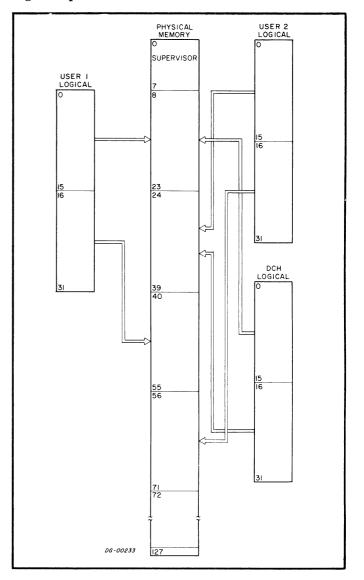

The MMPU feature of the NOVA 830 and 840 allows the allocation of memory to a user in blocks of 1024 words and up to 32 such blocks may be allocated to a user. A user is prohibited from accessing those blocks of memory not allocated to him, thus protecting a user's area of memory from unauthorized access. The MMPU feature allows areas of memory to be write-protected and areas of memory to be allocated to more than one user, thus allowing the sharing of data and procedure areas. The blocks of memory allocated to a user do not have to be contiguous.

The address translation function which correlates a logical address to the corresponding allocated physical memory address is called an "address map". The MMPU feature holds one user map at a time, but it has the capability of simultaneously mapping memory references for the data channel with a different map.

In addition to translating addresses, the feature also performs various protection functions. A user is allowed to access only those blocks of memory allocated to him. This ensures that a user does not reach out of his own areas of memory for either instructions or data. Blocks of memory allocated to a user may be write-protected so that the user may not modify them. This allows blocks of memory containing constants or nonselfmodifying procedures to be shared between users. The MMPU feature detects and inhibits indirection chains that go deeper than 16 levels. This protects the system from becoming disabled by an indirection loop. The MMPU allows devices to be declared accessible or inaccessible to a user on an individual device code basis. This allows any device to be controlled by the operating system or dedicated to a user, depending upon user requirements.

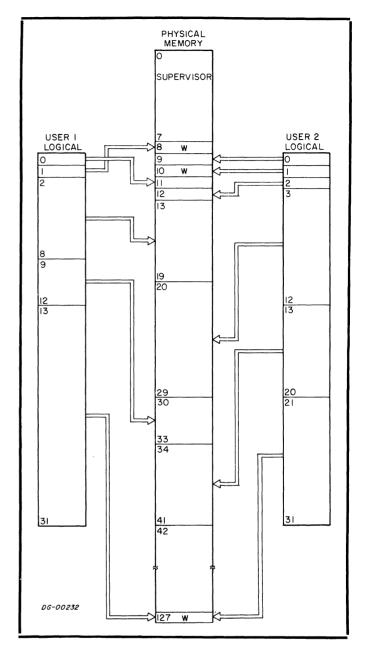

The MMU allows the allocation of memory to a program in the same manner as the NOVA 830 and 840 MMPU, but performs no protection functions. In addition, the MMU can hold two program maps and two data channel maps at the same time. Only one program map can be enabled at any one time, but both data channel maps are enabled at the same time.

The NOVA 3/D MMU and MPU combination allows the allocation of memory to a program in the same manner as the NOVA 830 and 840 MMPU. Like the MMU, the NOVA 3/D MMU and MPU can hold two program maps and two data channel maps at the same time. Only one program map can be enabled at any one time, but both data channel maps are enabled at the same time.

The NOVA 3/D MMU and MPU protection functions are similar to those provided by the NOVA 830 and 840 MMPU. The NOVA 3/D combination, however, does not allow individual devices to be declared inaccessible to a user. Instead, the I/O protection feature allows all devices to be declared accessible or inaccessible to a user.

#### Memory

Memory is available in many forms for the different members of the NOVA line. For the NOVA computer, core memory is available in modules of 2, 4, and 8K 16-bit words. For the SUPERNOVA computer, memory is available in both core and semiconductor forms. Core memory is available in modules of both 4 and 8K 16-bit words. Semiconductor memory is available in both read/write and read-only forms in modules of 256, 512, and 1024 16-bit words. For the NOVA 1200 series of computers, both core and semiconductor memory is available. Core memory is available in modules of 4, 8, and 16K 16-bit words. Semiconductor memory is available in both read/write and readonly forms in modules of 256, 512, and 1024 16-bit words. For the NOVA 800 and 820 computers, core memory is available in modules of 4 and 8K 16-bit words. For the NOVA 830 computer, core memory is available in modules of 16K 16-bit words. For the NOVA 840 computer, core memory is available in modules of 8K 16-bit words. For the NOVA 2 series of computers, core memory is available in modules of 4, 8, and 16K 16-bit words. For the NOVA 3 series of computers, memory is available in both core and semiconductor forms.

Core memory is available in modules of both 8 and 16K 16-bit words. Semiconductor memory is available in modules of 4K, 8K, 16K and 32K 16-bit words.

In addition, a memory parity option is available with the NOVA 3 series which will detect any single bit error in a word read from main memory. If desired, the parity option can interrupt the central processor upon finding an error. This allows a record to be kept of memory errors.

#### Auto-Increment/Decrement

If the intermediate address of a short class instruction is in the range  $20-27_8$ , and the indirect bit is 1, the contents of the addressed location are incremented by one. The incremented value is used to continue the addressing chain.

If the intermediate address of a short class instruction is in the range  $30-37_8$ , and the indirect bit is 1, the contents of the addressed location are decremented by one. The decremented value is used to continue the addressing chain.

NOTE The state of bit 0 BEFORE the increment or decrement determines whether the indirection chain is continued. For example: Assume an auto-increment location contains 1777778 (all bits = 1 including bit 0), and the location is referenced as part of an indirection chain. After incrementing, the location contains all zeros. However, bit 0 was 1 before the increment, so 0 will be the next address in the chain, rather than the effective address.

#### Power Fail/Auto Restart

The power fail/auto restart feature of the NOVA line provides a "fail-soft" capability in the event of unexpected power loss. In the event of power failure, there is a delay of one to two milliseconds before the processor shuts down. The power fail portion of the feature senses the imminent loss of power and interrupts the processor. The interrupt service routine can then use this delay to store the contents of the accumulators, the program restart address, and other information that will be needed to restart the system. One to two milliseconds is enough time to execute 200 to 1500 instructions depending on the processor, so there is more than enough time to perform the power fail routine.

When power is restored, the action taken by the auto-restart portion of the feature depends upon the position of the power switch on the front panel. If the switch is in the "on" position, the processor remains stopped after power is restored. If the switch is in the 'lock' position, then 50 milliseconds after power is restored, the processor executes the instruction contained in the first location of main memory, restarting the interrupted system.

The battery backup option available with the NOVA 3 series operates in conjunction with the power fail/auto restart feature to provide security for semiconductor memories in the event of a power failure. If power fails, the battery backup option will supply power to the memories for a period of up to two hours so that they will not lose their data. If further security is desired, an external battery backup option is available so that the customer can connect larger batteries and ensure the integrity of the memories for extended periods of time.

#### **Real-Time Clock**

The real-time clock feature of the NOVA line computers generates a sequence of pulses that is independent of the timing of the processor. The clock will interrupt the system at one of four programselectable frequencies. The frequencies are: ac line frequency, 10Hz, 100Hz, and 1000Hz.

#### Input/Output Bus

The input/output (I/O) bus is that portion of the computer that carries commands and data between the central processor and various peripheral de-vices connected to it. The bus is made up of a six-line device selection network, interrupt circuitry, command circuitry, and sixteen data lines.

#### **Device Addressability**

Each I/O device in a NOVA line computer system is connected to the six-line device selection network in such a way that each device will only respond to commands that contain its own device code. The fact that the selection network is made up of six lines gives  $2^6 = 64$  unique device codes. Two of these codes are reserved for specific functions, but there are still 62 device codes available for use with I/O devices.

#### Interrupt Capability

The interrupt circuitry contained in the I/O bus provides the capability for any I/O device to interrupt the system when that device requires service. When a device requests an interrupt, the processor automatically transfers program control to the main interrupt service routine. This routine can either poll all the I/O devices in the system to find out which one initiated the interrupt or the routine can use a special instruction to identify the source of the interrupt.

The interrupt circuitry of the NOVA line also contains the capability to implement up to sixteen levels of priority interrupts. This is done with a 16-bit priority mask. Each level of device priority is associated with a bit in this mask. In order to suppress interrupts from any priority level, the corresponding bit in the mask is set to 1.

#### <u>Data Channel</u>

Handling data transfers between external devices and memory under program control requires an interrupt plus the execution of several instructions for each word transferred. To allow greater transfer rates, the I/O bus contains circuitry for a direct memory access (DMA) data channel through which a device, at its own request, can gain direct access to main memory using a minimum of processor time. At the maximum transfer rate, the data channel effectively stops the processor, but at lower rates, processing continues while data is being transferred.

#### Ease of Interfacing

Due to the straightforward logic and general design of the NOVA line I/O bus, customer-provided or customer-designed I/O devices may be easily interfaced to a NOVA line computer system. Information on how to interface to the NOVA line may be found in ''The Interface Designer's Reference Manual'' (DGC 015-000031).

#### Input/Output Devices

A comprehensive array of I/O devices is available from Data General for the NOVA line. This wide choice of devices, ranging from teletypewriters to line printers to video displays for man-machine interaction; and from paper tape to magnetic tape to fixed and moving-head discs for data storage allows a wide spectrum of possible configurations. Also available are various multiplexors and telecommunications adapters including an IBM 360/370 interface.

#### Software

The NOVA line is fully supported by proven Data General software. Because all members of the NOVA line are program compatible with each other, it is possible to create a computer system that can be easily altered or upgraded as the need arises.

#### Languages

In addition to an assembler and a macro-assembler, there are powerful higher-level language processors available for use with the NOVA line. Language processors such as ALGOL, EXTENDED BASIC, FORTRAN IV, and FORTRAN 5 can be used to ease the job of implementing application systems.

### **Operating Systems**

There is a wide array of operating systems available for the NOVA line. These range from the Stand-alone Operating System (SOS) to the Real-Time Operating System (RTOS) to the Real-Time Disc Operating System (RDOS), to the Mapped Real-Time Disc Operating System (MRDOS). SOS, RTOS, and RDOS software are designed for the small to medium-size systems, while MRDOS software is designed for the large system and gives full software support for the Memory Management and Protection Unit.

### Conclusion

The internal features, software, and I/O devices available with the NOVA line of computers ensure that they will easily meet the continually changing needs of the data processing industry.

# SECTION II INTERNAL STRUCTURE

### INTRODUCTION

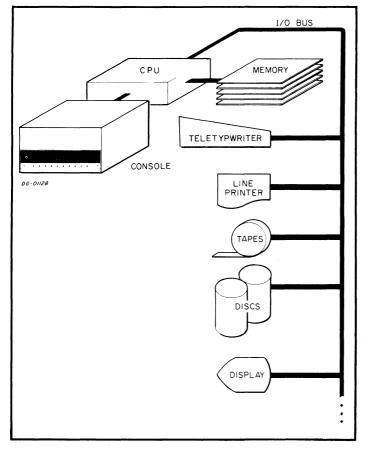

The basic structure of a NOVA line data processing system consists of a central processing unit (CPU), some amount of main memory, the I/O bus, the I/O devices connected to the I/O bus, and a console which is on the front panel of the main computer chassis.

Due to the general-purpose design of the NOVA line, the type, size, and number of memory modules and I/O devices have no effect upon the internal logical structure of the CPU. This chapter

deals with the addressing of information and the logical representation of information within the CPU, and is unaffected by those portions of the system outside the CPU.

### **INFORMATION FORMATS**

The basic piece of information within the processor is the binary digit, or "bit". A bit is capable of representing only two quantities, 0 and 1. However, a bit cannot represent both these values at the same time. At any one point in time, a bit can either represent a 0 or a 1, never both.

The normal unit of information within the CPU is the "word". A word is made up of 16 bits. Because each bit is capable of representing two quantities, a word is capable of representing  $2^{16} = 65,536$  different quantities. A word may be broken into two "bytes" of 8 bits each. A byte is capable of representing  $2^8 = 256$  different quantities. I/O devices transfer information in units of bits, bytes, words or groups of words called "records" depending upon the device.

### **Bit Numbering**

In order to avoid confusion when talking about the information contained in bytes and words, the bits that make up these units of information are numbered from left to right, with the leftmost (high-order) bit always numbered bit 0. The numbering extends to the right and is always carried out in the decimal number system. The rightmost (low-order) bit in a byte is bit 7. The rightmost bit in a word is bit 15.

| wo       | RD   | wo              | RD                                         |

|----------|------|-----------------|--------------------------------------------|

| BYTE     | BYTE | BYTE            | BYTE                                       |

| 01234567 |      | 0   2 3 4 5 6 7 | 0, 1, 2, 3, 4, 5, 6, 7<br>8 91011 12131415 |

#### **Octal Representation**

Because talking about the binary data contained in bytes and words would quickly become awkward and confusing if each bit were described, the octal representation of binary information will be used in this manual. To convert a piece of binary information to its octal representation, the bits in the quantity are separated into groups of three bits each, starting from the right and proceeding to the left. If the number of bits to be represented is not evenly divisible into groups of three, the leftmost group will contain one or two bits. Each group of bits can now be represented by one of eight different symbols. The digits 0-7 are used to represent the quantities 0-7. Each encoded digit is called an octal digit. Because each group of bits can contain any one of 8 values, this representation is sometimes called "base 8" representation.

Another way to represent binary information is the hexadecimal or "hex" representation. In hexadecimal, the bits in the quantity are separated into groups of four bits each and each group can be represented by one of 16 different symbols. The digits 0-9 are used to represent the quantities 0-9. The letters A-F are used to represent the quantities 10-15. Because each group of bits can contain any one of 16 values, this representation is sometimes called "base 16" representation.

| The following table gives the correspondence be- |

|--------------------------------------------------|

| tween the various representations.               |

| DECIMAL       | BINARY | HEX           | BINARY | OCTAL |

|---------------|--------|---------------|--------|-------|

| 0             | 0000   | 0             | 000    | 0     |

| 1             | 0001   | 1             | 001    | 1     |

| $\frac{1}{2}$ | 0010   | $\frac{1}{2}$ | 010    | 2     |

| 3             | 0011   | 3             | 011    | 3     |

| 4             | 0100   | 4             | 100    | 4     |

| 5             | 0101   | 5             | 101    | 5     |

| 6             | 0110   | 6             | 110    | 6     |

| 7             | 0111   | 7             | 111    | 7     |

| 8             | 1000   | 8             | 1 100  | 10    |

| 9             | 1001   | 9             | 1 001  | 11    |

| 10            | 1010   | Α             | 1 010  | 12    |

| 11            | 1011   | В             | 1 011  | 13    |

| 12            | 1100   | C             | 1 100  | 14    |

| 13            | 1101   | D             | 1 101  | 15    |

| 14            | 1110   | Е             | 1 110  | 16    |

| 15            | 1111   | F             | 1 111  | 17    |

Our normal decimal numbering system is sometimes called "base 10" representation. Because it is sometimes possible to confuse numbers written in hex or octal with those written in decimal, a subscript denoting the base will be used in cases where confusion might occur. The following examples illustrate this convention.

$$64_{10} = 40_{16} = 100_8$$

$$87_{10} = 57_{16} = 127_8$$

$$63_{10} = 3F_{16} = 77_8$$

In the last example, it is obvious that 3F is a number written in hex, but the subscript is included to erase any possible doubts.

Conversion tables for hex to decimal and octal to decimal are contained in Appendix B of this manual.

#### **Character Codes**

Within the processor, all information is represented by binary quantities. The CPU does not recognize certain bit combinations as characters and certain other bit combinations as numbers. Sooner or later, however, this information must be transferred outside the computer in some form easily understood by humans. For this reason, some standard correspondence must be made between certain bit combinations and printable symbols. The code used to implement this correspondence in I/O devices available with the NOVA line is called the American Standard Code for Information Interchange (ASCII). This code can represent 95 printable symbols plus 33 control functions. A complete table of the codes and their corresponding characters can be found in Appendix C of this manual.

#### Information Representation

Even though the CPU does not intrinsically recognize one information type from another, the different instructions in the instruction set expect that the information to be operated on will be in a specific format. In general, there are four different, basic information formats. They are integers, floating point numbers, logical quantities, and decimal numbers.

#### Integers

Integers can be represented as either signed or unsigned numbers and carried in either single or multiple precision. Single precision integers are two bytes long, while multiple precision integers are four or more bytes long. Unsigned integers use all the available bits to represent the magnitude of the number. A single two-byte word can represent any unsigned number in the inclusive range 0 to 65,535. Two words taken together as an unsigned, double precision integer can represent any number in the inclusive range 0 to 4,294,967,295.

For signed operations, the two's complement numbering system is used. In this system, the leftmost or high-order bit is used as a sign bit. If the sign bit is 0, the number is positive and the remainder of the bits in the number represent the magnitude of the number as described above. If the sign bit is 1, the number is negative and the remainder of the bits represent the two's complement of the magnitude of the number.

To create the negative of a number in the two's complement scheme, complement all the bits of the number including the sign bit. After the complementing process is finished, add 1 to the rightmost or low-order bit. If the two's complement of a negative number is formed, the result will be the corresponding positive number. There is only one representation for zero in two's complement arithmetic: it is the number with all bits zero. Forming the two's complement of zero will produce a carry out of the high-order bit and leave the number with all bits zero.

#### Examples:

To form the negative of 4:

| 4 =          | 0 | 000 | 000 | 000 | 000 | 100 |

|--------------|---|-----|-----|-----|-----|-----|

| complement = | 1 | 111 | 111 | 111 | 111 | 011 |

| add 1 +      |   |     |     |     |     | 1   |

| -4 =         | 1 | 111 | 111 | 111 | 111 | 100 |

To form the negative of  $1715_8$ :

| $1715_8 = 0$              | 000 | 001 | 111 | 001 | 101      |

|---------------------------|-----|-----|-----|-----|----------|

| complement = 1<br>add 1 + | 111 | 110 | 000 | 110 | 010<br>1 |

| $-1715_8 = \overline{1}$  | 111 | 110 | 000 | 110 | 011      |

To form the negative of  $-1715_{g}$ :

| -1715 <sub>8</sub> =   | 1 | 111 | 110 | 000 | 110 | 011             |

|------------------------|---|-----|-----|-----|-----|-----------------|

| complement = add 1 + t | 0 | 000 | 001 | 111 | 001 | 100             |

| $1715_{8} =$           | 0 | 000 | 001 | 111 | 001 | $\frac{1}{101}$ |

To form the negative of 0:

| 0 =          | 0 | 000 | 000 | 000 | 000 | 000 |

|--------------|---|-----|-----|-----|-----|-----|

| complement = | 1 | 111 | 111 | 111 | 111 | 111 |

| add 1 + 0 =  | 0 | 000 | 000 | 000 | 000 | 000 |

Note that 0 is a positive number, i.e., its sign bit is 0.

Because the two's complement scheme has only one representation for 0, there is always one more negative number than there are non-negative numbers. The most negative number is a number with a 1 in the sign bit and all other bits 0. The positive value of this number can not be represented in the same number of bits as used to represent the negative number.

A single two-byte word can represent any signed number in the inclusive range -32,768 to +32,767. Two words taken together as a signed, double precision integer can represent any number in the inclusive range -2,147,483,648 to +2,147,483,647.

It is a property of numbers using the two's complement scheme that addition and subtraction of signed numbers are identical to addition and subtraction of unsigned numbers. The CPU just treats the sign bit as the most significant magnitude bit.

#### **Floating Point**

The floating point feature of the NOVA line allows operations on signed numbers having a much larger range than those normally represented as integers. It would take a 16-word multiple precision integer to represent the range of a NOVA line floating point number. Since floating point numbers occupy either two words for single precision or four words for double precision, and the floating point feature is much faster than multiple precision integer software routines, floating point arithmetic is used when numbers having a large range must be manipulated.

A floating point number is made up of three parts: the sign, the exponent, and the mantissa. The value of a floating point number is defined to be:

(MANTISSA) X (16 RAISED TO THE TRUE VALUE OF THE EXPONENT FIELD)

The number is signed according to the value of the sign bit. If the sign bit is 0, the number is positive; if the sign bit is 1, the number is negative.

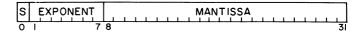

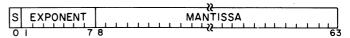

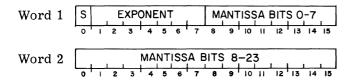

Floating point numbers are represented internally by either 32 bits (single precision) or 64 bits (double precision). The formats are shown below:

#### **Single Precision**

#### **Double Precision**

Bit zero is the sign bit: 0 for positive, 1 for negative.

Bits 1-7 contain the exponent. This is the power to which 16 must be raised in order to give the correct value to the number. So that the exponent field may accommodate a large range, "Excess 64" representation is used. This means that the value in the exponent field is 64 greater than the true value of the exponent. If the exponent field is zero, the true value of the exponent is -64. If the exponent field is 64, the true value of the exponent is 0. If the exponent field is 127, the true value of the exponent is 63.

Bits 8-31 for single precision and bits 8-63 for double precision contain the mantissa. This means that bit 8 of the floating point number is bit 0 of the mantissa. The mantissa is always a positive fraction greater than or equal to 1/16 and less than 1. The "binary point" can be thought of as being just to the left of bit 8. Continuing this concept then, bit 8 represents the value 1/2, bit 9 represents the value 1/4, bit 10 represents the value 1/8, and so on.

In order to keep the mantissa in the range of 1/16 to 1, the results of floating point arithmetic are "normalized". Normalization is the process whereby the mantissa is shifted left one hex digit at a time until the high-order four bits represent a nonzero quantity. For every hex digit shifted, the exponent is decreased by one. Since the mantissa is shifted four bits at a time, it is possible for the high-order three bits of a normalized mantissa to be zero. Zero is represented by a floating point number with all bits zero. This is true for both single and double precision. This is known as "true zero". When a calculation results in a zero mantissa, the floating point processor automatically converts the number to a true zero. Note that true zero is positive. It is not possible to obtain negative zero as the result of a calculation.

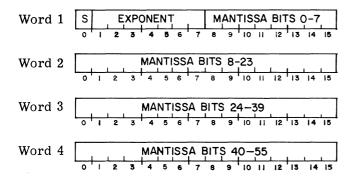

Floating point operands in memory are represented by two words for single precision and by four words for double precision. The formats are shown below:

#### **Single Precision**

#### **Double Precision**

#### **Logical Quanities**

Logical operations in the NOVA line can be performed upon individual bits, bytes, or words. When using the logical operations, quantities operated on are treated as unstructured binary quantities. The number of bits, bytes, or words operated upon depends on the particular instruction.

#### **Decimal Numbers**

Decimal numbers may be represented internally in two ways, character decimal and packed decimal. In character decimal, the number is made up of a string of ASCII characters and the sign, if present, may appear in one of four places. The sign of the number may be indicated by a leading or trailing byte which contains the ASCII code for plus  $(2B_{16})$ or minus  $(2D_{16})$ . Alternatively, either the highorder digit or the low-order digit of the number may indicate the sign in addition to carrying a digit of the number. The table below gives the correspondence between certain ASCII characters and the sign and digit values that they carry.

| SIGN<br>VALUE | DIGIT<br>VALUE | ASCII<br>CHARACTER | HEX<br>CODE |

|---------------|----------------|--------------------|-------------|

| +             | 0              | }                  | 7B          |

| +             | 1              | A                  | 41          |

| +             | 2              | В                  | 42          |

| +             | 3              | С                  | 43          |

| +             | 4              | D                  | 44          |

| +             | 5              | E                  | 45          |

| +             | 6              | F                  | 46          |

| +             | 7              | G                  | 47          |

| +             | 8              | Н                  | 48          |

| +             | 9              | Ι                  | 49          |

| -             | 0              | }                  | 7D          |

| -             | 1              | Ĵ                  | 4A          |

| -             | 2<br>3         | K                  | 4B          |

| -             |                | ${ m L}$           | 4C          |

| -             | 4              | Μ                  | 4D          |

| -             | 5              | Ν                  | 4E          |

| -             | 6              | 0                  | 4F          |

| -             | 7              | Р                  | 50          |

| -             | 8              | Q                  | 51          |

| -             | 9              | R                  | 52          |

The digits that are not carrying the sign must be valid ASCII characters for the digits 0-9  $({}^{30}16^{-39}16^{)}$ .

#### Examples:

In the following examples, the hex value of a byte is shown inside the box; the corresponding ASCII character is shown beneath the box.

| +2,048 (leading sign)    | 2B | 32 | 30 | 34 | 38 |

|--------------------------|----|----|----|----|----|

|                          | +  | 2  | 0  | 4  | 8  |

| -1,756 (trailing sign)   | 31 | 37 | 35 | 36 | 2D |

|                          | 1  | 7  | 5  | 6  | -  |

| +1,850 (high-order sign) | 41 | 38 | 35 | 30 |    |

|                          | Α  | 8  | 5  | 0  |    |

| -3,970 (low-order sign)  | 33 | 39 | 37 | 7D |    |

|                          | 3  | .9 | 7  | }  |    |

For packed decimal, each digit of the decimal number occupies one hex digit. The sign is specified by a trailing hex digit. The number must start and end on a byte boundary. In other words, the number cannot start or end halfway through a byte. This means that a packed decimal number will always consist of an odd number of digits followed by the sign. The sign must be either  $C_{16}$  for plus or  $D_{16}$  for minus. The only valid codes for digits are  $0-9_{16}$ .

Examples:

In the following examples, the hex value of a digit is shown within the box; the corresponding decimal digit is shown beneath the box.

|         | By | rte | Ву | rte | By | /te |

|---------|----|-----|----|-----|----|-----|

| + 2,048 | 0  | 2   | 0  | 4   | 8  | С   |

|         | 0  | 2   | 0  | 4   | 8  | +   |

| +32,456 | 3  | 2   | 4  | 5   | 6  | С   |

|         | 3  | 2   | 4  | 5   | 6  | +   |

| - 1,756 | 0  | 1   | 7  | 5   | 6  | D   |

|         | 0  | 1   | 7  | 5   | 6  | -   |

| -25,989 | 2  | 5   | 9  | 8   | 9  | D   |

|         | 2  | 5   | 9  | 8   | 9  | -   |

## INFORMATION ADDRESSING

The information formats described in the preceding section give a way of representing different types of data in main memory. Operations cannot be performed upon these data types, however, unless they can be addressed by the CPU. The address of a piece of information is its location in main memory. Once the CPU knows the address of a piece of information, the desired operation can be performed.

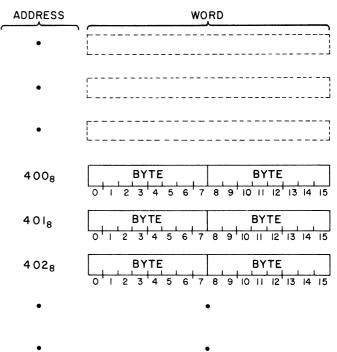

#### Word Addressing

Main memory is partitioned into 2-byte words, and each word has an address. The first word in mem-

ory has the address 0. The next word has the address 1, the next word has the address 2, and so on. Word addressing is used to address integers, floating point numbers, and logical quantities that are formatted in units of words.

DG-00538

#### **Effective Address Calculation**

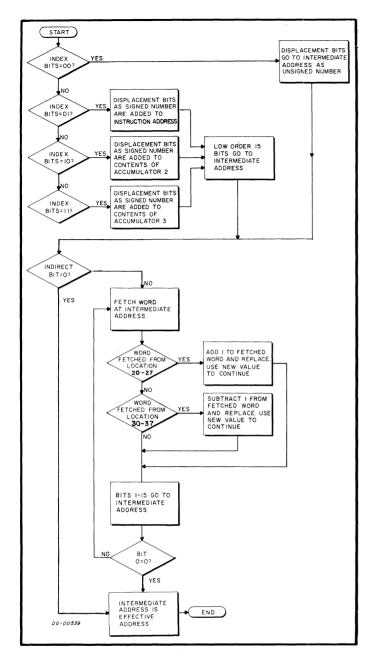

There are six instructions in the NOVA line instruction set that directly reference memory using word addressing. These instructions use eleven bits in the instruction to define the address of the desired word. These eleven bits do not directly specify the address, but are used in a calculation which results in the address of the desired word. The resultant address is called the "effective address" or "E", and the calculation is called the "effective address calculation".

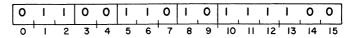

The eleven bits in an instruction that are used in the effective address calculation, are bits 5-15. Their format is shown below.

|   |   |   |   |   | @ | IND | PEX | DISPLACEMEN |   |    |    | Т  |    |    |    |

|---|---|---|---|---|---|-----|-----|-------------|---|----|----|----|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6   | 7   | 8           | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Bit 5 is called the "indirect bit", bits 6 and 7 are called the "index bits", and bits 8-15 are called the "displacement bits".

If the index bits are 00, the displacement is used as an unsigned 8-bit number to address one of the first  $256_{10}$  words in memory. This is called "page zero addressing" and this first block of 256 words is known as "page zero".

If the index bits are 01, the displacement is treated as a signed, two's complement number, which is added to the address of the instruction to produce a memory address. This is called "relative addressing". By relative addressing, any instruction which uses the effective address calculation can directly address any word in storage whose address is in the range  $-128_{10}$  to  $+127_{10}$  from the instruction.

If the index bits are 10, accumulator 2 is used as an index register. If the index bits are 11, accumulator 3 is used as an index register. In this form of word addressing, known as "index register addressing", the displacement is treated as a signed, two's complement number which is added to the contents of the selected index register to produce a memory address. In index register addressing, the addition of the displacement to the contents of index register does not change the value contained in the index register. The result of the addition performed in relative addressing and index register addressing is  $4\pi a$ . (a) "clipped" to 15 bits. In other words, the highorder bit of the result is set to 0. For example, if accumulator 2 is to be used as an index register and contains the number  $077774_8$ , and the displacement bits contain the number  $012_8$ , then the result of the addition would be  $000006_8$ , not  $100006_8$ .

After one of the three types of addresses has been computed from the index and displacement bits, the indirect bit is tested. If this bit is zero, the address already computed is taken as the effective address. If the indirect bit is one, the word addressed by the result of the index and displacement bits is assumed to contain an address. In this word bit 0 is the indirect bit and bits 1-15 contain an address. If bit 0 of the referenced word is 1, another level of indirection is indicated, and bits 1-15 contain the address of the next word in the indirection chain. The processor will continue to follow this chain of indirect addresses until a word is retrieved with bit 0 set to 0. Bits 1-15 of this word are taken to be the effective address.

#### Auto-Increment/Decrement