**Customer Documentation**

# Technical Notice for AViiON<sup>™</sup> 3000 and 4000 Series Systems: Programming System Control and I/O Registers

# Technical Notice for AViiON <sup>™</sup>3000 and 4000 Series Systems: Programming System Control and I/O Registers

014-001878-00

Ordering No. 014-001878 Copyright © Data General Corporation, 1990 All Rights Reserved Printed in the United States of America Rev. 00, June 1990

# Notice

DATA GENERAL CORPORATION (DGC) HAS PREPARED THIS DOCUMENT FOR USE BY DGC PERSONNEL, CUSTOMERS, AND PROSPECTIVE CUSTOMERS. THE INFORMATION CONTAINED HEREIN SHALL NOT BE REPRODUCED IN WHOLE OR IN PART WITHOUT DGC'S PRIOR WRITTEN APPROVAL.

DGC reserves the right to make changes in specifications and other information contained in this document without prior notice, and the reader should in all cases consult DGC to determine whether any such changes have been made.

THE TERMS AND CONDITIONS GOVERNING THE SALE OF DGC HARDWARE PRODUCTS AND THE LICENSING OF DGC SOFTWARE CONSIST SOLELY OF THOSE SET FORTH IN THE WRITTEN CONTRACTS BETWEEN DGC AND ITS CUSTOMERS. NO REPRESENTATION OR OTHER AFFIRMATION OF FACT CONTAINED IN THIS DOCUMENT INCLUDING BUT NOT LIMITED TO STATEMENTS REGARDING CAPACITY, RESPONSE-TIME PERFORMANCE, SUITABILITY FOR USE OR PERFORMANCE OF PRODUCTS DESCRIBED HEREIN SHALL BE DEEMED TO BE A WARRANTY BY DGC FOR ANY PURPOSE, OR GIVE RISE TO ANY LIABILITY OF DGC WHATSOEVER.

IN NO EVENT SHALL DGC BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL OR CONSEQUENTIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS) ARISING OUT OF OR RELATED TO THIS DOCUMENT OR THE INFORMATION CONTAINED IN IT, EVEN IF DGC HAS BEEN ADVISED, KNEW OR SHOULD HAVE KNOWN OF THE POSSIBILITY OF SUCH DAMAGES.

CEO, DASHER, DATAPREP, DESKTOP GENERATION, ECLIPSE, ECLIPSE MV/4000, ECLIPSE MV/6000, ECLIPSE MV/8000, GENAP, INFOS, microNOVA, NOVA, PRESENT, PROXI, SWAT, and TRENDVIEW are U.S. registered trademarks of Data General Corporation; and AOSMAGIC, AOS/VSMAGIC, AROSE/PC, ArrayPlus, AViiON, BaseLink, BusiGEN, BusiPEN, BusiTEXT, CEO Connection, CEO Connection/LAN, CEO Drawing Board, CEO DXA, CEO Light, CEO MAILI, CEO Object Office, CEO PXA, CEO Wordview, CEOwrite, COBOL/SMART, COMPUCALC, CSMAGIC, DASHER/One, DASHER/286, DASHER/286-12c, DASHER/386, DASHER/386-16c, DASHER/386-25, DASHER/386sx, DASHER/LN, DATA GENERAL/One, DESKTOP/UX, DG/500, DG/AROSE, DGConnect, DG/DBUS, DG/Fontstyles, DG/GATE, DG/GEO, DG/HEO, DG/L, DG/LIBRARY, DG/UX, DG/XAP, ECLIPSE MV/1000, ECLIPSE MV/1400, ECLIPSE MV/2000, ECLIPSE MV/2500, ECLIPSE MV/1000, ECLIPSE MV/15000, ECLIPSE MV/7800, ECLIPSE MV/2000, ECLIPSE MV/10000, ECLIPSE MV/15000, ECLIPSE MV/2000, ECLIPSE MV/2000, ECLIPSE MV/10000, FORMA-TEXT, GATEKEEPER, GDC/1000, GDC/2400, microECLIPSE, microMV, MV/UX, PC Liaison, RASS, REV-UP, SLATE, SPARE MAIL, SUPPORT MANAGER, TEO, TEO/3D, TEO/Electronics, TURBO/4, UNITE, WALKABOUT, WALKABOUT/SX, and XODIAC are trademarks of Data General Corporation.

AT is a U.S. registered trademark of International Business Machines Corporation. Brooktree is a registered trademark of Brooktree Corporation. RAMDAC is a trademark of Brooktree Corporation. Timekeeper and Zeropower are trademarks of SGS-Thomson Microelectronics. X Window System is a trademark of the Massachusetts Institute of Technology.

> Technical Notice for AViiON<sup>™</sup> 3000 and 4000 Series Systems: Programming System Control and I/O Registers 014-001878-00 014-001879-00 (Japanese version)

Revision History: Original Release – June 1990

A vertical bar in the margin of a page indicates substantive technical change from the previous revision.

# How to Use this Technical Notice

Use this technical notice in conjunction with the programming manual AViiON<sup>™</sup> 300 and 400 Series Stations: Programming System Control and I/O Registers (014-001800) to program 3000 and 4000 series systems. These pages identify how a 3000 or 4000 series system differs from 300 and 400 series stations. Insert these pages into the programming manual as described in the section "Updating Instructions" that follows.

This technical notice affects the programming manual as follows:

| Chapter 1  | System Board Architecture<br>See changes enclosed.                                                                                                                                                                                                                                                       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 2  | Programming the System Board<br>Items or sections labeled 400 series only do apply to 3000 and<br>4000 series systems. Disregard items or sections labeled 300<br>series only, they do not apply to 3000 and 4000 series. All<br>addresses are the same as addresses for 400 series systems.             |

| Chapter 3  | Interrupts, System Errors and Bus Faults<br>Items or sections labeled 400 series only do apply to 3000 and<br>4000 series systems. Disregard items or sections labeled 300<br>series only, they do not apply to 3000 and 4000 series. All<br>addresses are the same as addresses for 400 series systems. |

| Chapter 4  | Programming the Monochrome Graphics Subsystem<br>Because the 3000 and 4000 series stations do not support<br>graphics, disregard this chapter.                                                                                                                                                           |

| Chapter 5  | Programming the Color Graphics Subsystem<br>Because the 3000 and 4000 series stations do not support<br>graphics, disregard this chapter.                                                                                                                                                                |

| Chapter 6  | Programming the Keyboard Interface and Speaker<br>Because the 3000 and 4000 series stations do not support a<br>keyboard, disregard this chapter.                                                                                                                                                        |

| Chapter 7  | Programming the Serial Ports and Parallel Port<br>See changes enclosed.                                                                                                                                                                                                                                  |

| Chapter 8  | Programming the Local Area Network<br>No changes.                                                                                                                                                                                                                                                        |

| Chapter 9  | Programming the Small Computer System Interface No changes.                                                                                                                                                                                                                                              |

| Appendix A | Address Map<br>No changes.                                                                                                                                                                                                                                                                               |

| Appendix B | Power-up Flowchart<br>No changes.                                                                                                                                                                                                                                                                        |

| Appendix C | Boot File Format<br>No changes.                                                                                                                                                                                                                                                                          |

| Appendix D | System Board Connectors<br>See changes enclosed.                                                                                                                                                                                                                                                         |

# **Updating Instructions**

To update your copy of  $AViiON^{\text{TM}}$  300 and 400 Series Stations: Programming System Control and I/O Registers, please remove the pages from the manual and insert the technical notice pages into the manual as follows:

| Remove            | Insert            |

|-------------------|-------------------|

| Contents          | Contents          |

| Tables            | Tables            |

| Figures           | Figures           |

| 1–1 through 1–4   | 1–1 through 1–4   |

| 1-9/1-10          | 1-9/1-10          |

| 2-7/2-8           | 2-7/2-8           |

| 2-15/2-16         | 2-15/2-16         |

| 3-1/3-2           | 3-1/3-2           |

| 3-11 through 3-16 | 3-11 through 3-16 |

| 7–1 through 7–2   | 7–1 through 7–2   |

| D–1 through D–6   | D–1 through D–6   |

| D-11/D-12         | D-11/D-12         |

Insert the Cover page immediately after the Cover page of the manual.

Insert the Title/Notice page immediately after the Title/Notice page of the manual.

Insert "How to Use this Technical Notice" immediately after the Preface of the manual.

· .

# Contents

# Chapter 1 – System Board Architecture

| Architecture and Configuration 1-2                |

|---------------------------------------------------|

| System Board Architecture and Configuration 1-3   |

| The CPU Set 1-5                                   |

| The CPU                                           |

| The Cache/Memory Management Unit (CMMU) 1-6       |

| Memory 1-9                                        |

| Main Memory                                       |

| Main-Memory Interface                             |

| Battery Backed Up (BBU) SRAM and PROM 1-10        |

| The System Control Logic 1-11                     |

| The Mbus and the Sbus 1-12                        |

| The Mbus                                          |

| The Sbus                                          |

| The Mbus/Sbus Interface 1-13                      |

| The Graphics Subsystem                            |

| Monochrome Graphics 1-14                          |

| Color Graphics                                    |

| Z-Buffer Controller 1-15                          |

| The I/O Subsystem                                 |

| Keyboard Port                                     |

| Mouse Port                                        |

| Serial Ports                                      |

| Parallel Port                                     |

| Small Computer Systems Interface (SCSI) Port 1-15 |

| Local Area Network (LAN) Interface                |

| The VMEbus Interface (400 Series Only) 1-16       |

| Registers                                         |

| Timers Available to System Programmers 1-19       |

| Interrupts and the Interrupt Logic 1-19           |

# Chapter 2 – Programming the System Board

| Programming the CPU 2-2                                 |

|---------------------------------------------------------|

| Addressing Memory 2-3                                   |

| Data Transfers to/from Memory 2-3                       |

| Address Map 2-4                                         |

| Mbus and Sbus 2-5                                       |

| Mbus and Sbus Arbitration                               |

| Master and Slave Devices                                |

| Data Alignment                                          |

| Addressing System Board Resources and System Memory 2-7 |

| Addressing VME Controllers (400 Series Only) 2-9        |

| Addressing System Board Resources from a VME Controller (400 Series Only) . | 2-12 |

|-----------------------------------------------------------------------------|------|

| Programming the System Control Registers                                    | 2-16 |

| The Time-of-Boot (TOB) Clock and Nonvolatile RAM (NOVRAM)                   | 2-23 |

| Programming the CIO                                                         | 2-25 |

| The Boot PROM                                                               | 2-26 |

| Power-Up and Boot Code                                                      | 2-26 |

| The System Control Monitor (SCM)                                            | 2-27 |

# Chapter 3 – Interrupts, System Errors, and Bus Faults

| Types of Interrupts                                |

|----------------------------------------------------|

| Condition–Specific Interrupts 3–2                  |

| Multiple-Use Interrupts (3000 and 4000 Series) 3-2 |

| How the CPU Is Interrupted 3-3                     |

| Handling Interrupts 3-4                            |

| Programming the CPU Interrupt Registers            |

| 300 Series CPU Interrupt Registers 3-7             |

| 3000 and 4000 Series CPU Interrupt Registers       |

| Programming the VME Interrupt Registers            |

| IRQ[7-0] Level Interrupts 3-24                     |

| System Errors                                      |

| Bus Faults                                         |

# Chapter 4 – Programming the Monochrome Graphics Subsystem

# Chapter 5 – Programming the Color Graphics Subsystem

| Features of the Color Graphics Subsystem       |

|------------------------------------------------|

| Components of the Color Graphics Subsystem 5-2 |

| The Color Graphics Controller                  |

| The Frame Buffer                               |

| RAMDAC                                         |

| The Clock Generator                            |

| The Z-Buffer                                   |

| Programming Conventions                        |

| Handshaking                                    |

| Context Switching 5-8                          |

| Accessing Color Graphics Resources 5-9         |

| Fixed-Point Numbers 5-13                       |

| Interrupts                                     |

| Registers                                      |

| Global Registers                               |

| Command and Status Registers                   |

| Color graphics Commands 5-35                   |

| Programming the Frame Buffer (8-bit) 5-56      |

| Accessing the Frame Buffer 5-57                |

| Frame Buffer Access Restrictions               |

| Programming the Lookup Table                   |

| Automatic LUT Load (ALL) Function              |

| Blinking                                       |

| Double-Buffering 5-59                          |

| Accessing the RAMDAC                           |

| Initializing the Registers                     |

| Programming the Z-Buffer Controller 5-72       |

| Components of the Z-Buffer 5-72                |

| Programming the Z-Buffer Registers 5-74        |

# Chapter 6 – Programming the Keyboard Interface and Speaker

| Overview                             |

|--------------------------------------|

| Components of the Keyboard Interface |

| UART                                 |

| Clock and Timing Logic 6-2           |

| Keyboard Speaker                     |

| Keyboard Connector                   |

| Programming the Keyboard Interface   |

| Clock and Data Lines                 |

| Data Format                          |

| Registers                            |

| Keyboard Scan Codes                  |

| Interrupts                           |

| Receiving Data from the Keyboard     |

| Transmitting Data to the Keyboard    |

| Programming the Speaker              |

# Chapter 7 – Programming the Serial Ports and Parallel Port

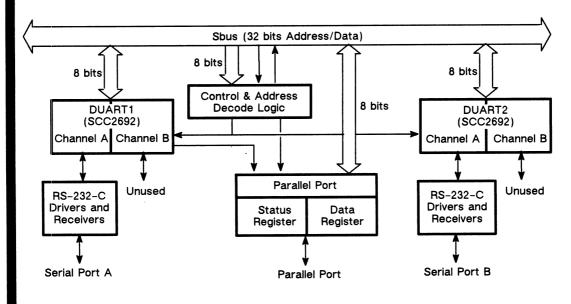

| Overview of the Serial and Parallel Ports           |

|-----------------------------------------------------|

| Components of the Serial and Parallel Ports         |

| DUART                                               |

| Parallel Port                                       |

| Programming the Serial Ports                        |

| Initializing the Serial Ports                       |

| Resetting the Serial Ports                          |

| Interrupts                                          |

| Programming the Mouse Port                          |

| Initializing the Mouse Port                         |

| Data Protocol                                       |

| Tracking Software                                   |

| Programming Hints                                   |

| Sensitivity                                         |

| Programming the Parallel Port                       |

| Registers                                           |

| Interrupts and Transmitting Data                    |

| Programming the Data Strobe and Data Select Signals |

# Chapter 8 – Programming the Local Area Network Interface

| Components of the LAN Interface               |

|-----------------------------------------------|

| Sbus Interface                                |

| Address Extension Logic 8-3                   |

| Ethernet Controller                           |

| Serial Interface                              |

| AUI Connector and Cable 8-3                   |

| Medium Attachment Unit (MAU) 8-3              |

| Ethernet Frame Transfers                      |

| Incoming Frame Path                           |

| Outgoing Frame Path                           |

| Programming the LAN Interface                 |

| Programming the Ethernet Controller Registers |

| Allocating Memory to the LAN Interface        |

| LAN Interface Data Structures                 |

| Software Environment                          |

| Initializing the LAN Interface                |

| Resetting the LAN Interface                   |

| LAN Interface Interrupts 8-17                 |

## Chapter 9 – Programming the Small Computer System Interface Port

| Overview of the SCSI Port                      |

|------------------------------------------------|

| Components of the SCSI Port                    |

| SCSI Slave Interface                           |

| SCSI Protocol Controller                       |

| DMA Controller                                 |

| Programming the SCSI Controller                |

| Resetting and Initializing the SCSI Controller |

| SCSI Controller Interrupts                     |

| Programming the DMA Controller                 |

| Manipulating Pointers and Counters             |

| Implementing a Selection Time-Out Function     |

| DMA Controller Interrupts                      |

## Appendix A – Address Map

## Appendix B – Power–Up Flowchart

Appendix C – Boot File Format

### Appendix D – System Board Connectors

Index

**Documentation Set**

· .

# **Tables**

#### Table

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5 | System Configurations1-2CPU Clock Frequencies and Periods1-6Memory Read and Write Cycles1-10Mbus Signals1-12Sbus Signals1-13 |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| 1-6<br>2-1                      | VMEbus Signals         1-17           System Memory Space         2-4                                                        |

| 2-2<br>2-3                      | Sbus Master Priorities       2-5         Address Modifiers (VME Space)       2-11                                            |

| 2-3<br>2-4                      | Address Modifiers (Transfer Type)                                                                                            |

| 2-5                             | Memory Map of the System Control Registers                                                                                   |

| 2-6                             | Memory Map for the Time-of-Boot Clock Registers 2-23                                                                         |

| 2-7                             | NOVRAM Addresses                                                                                                             |

| 2-8                             | CIO Register Addresses                                                                                                       |

| 2-9                             | SCM System Calls                                                                                                             |

|                                 | SCM Subroutines                                                                                                              |

| 3-1<br>3-2<br>3-3               | Memory Map of the Interrupt Registers                                                                                        |

|                                 | Monochrome Graphics Controller Commands                                                                                      |

|                                 | Frame Buffer Size                                                                                                            |

|                                 | Color Graphics Registers                                                                                                     |

| 5-4                             | Color Graphics Command Bits                                                                                                  |

| 5-5                             | Color Graphics Register Set Address Map 5-74                                                                                 |

| 6-1                             | Keyboard Signals                                                                                                             |

| 6-2                             | Keyboard Clock and Data Lines                                                                                                |

| 6-3<br>6-4                      | Keyboard Data Format                                                                                                         |

| 6-4<br>6-5                      | Keyboard Register Addresses                                                                                                  |

| 6-6                             | Commands                                                                                                                     |

| 6-7                             | Scan Code Sets 2 and 3 6-12                                                                                                  |

| 6-8                             | Speaker Register Addresses                                                                                                   |

| 7-2<br>7-3                      | Serial Port Register Addresses7-5Baud Rate Generator Characteristics7-8Mouse Data Protocol7-19Addresses of Parallel Port Registers7-21 |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

|                                 | Required LAN Register Configurations                                                                                                   |

|                                 | Memory Map of the Protocol Controller Registers                                                                                        |

| A-1<br>A-2                      |                                                                                                                                        |

| D-1<br>D-2<br>D-3<br>D-4<br>D-5 | Serial Connector Signals (400 Series)       D-6         Parallel Connector Signals (300 Series)       D-7                              |

| D-6                             | Parallel Connector Signals (400 Series)       D-7         Keyboard Signals       D-8                                                   |

| D-7<br>D-8                      | Speaker Signals    D-8      Mouse Signals    D-8                                                                                       |

| D-9                             |                                                                                                                                        |

| <b>D-1</b> 0                    |                                                                                                                                        |

| D-11                            |                                                                                                                                        |

| D-12                            | LAN Interface Connector Signals D-11                                                                                                   |

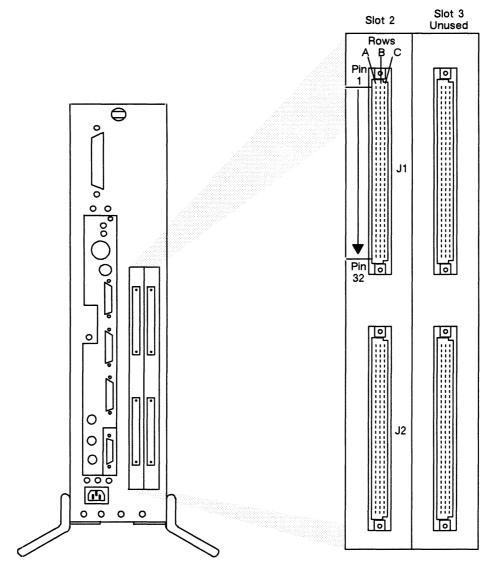

| D-13                            | VMEbus Connector J1 D-13                                                                                                               |

|                                 | VMEbus Connector J2 D-14                                                                                                               |

# **Figures**

#### Figure

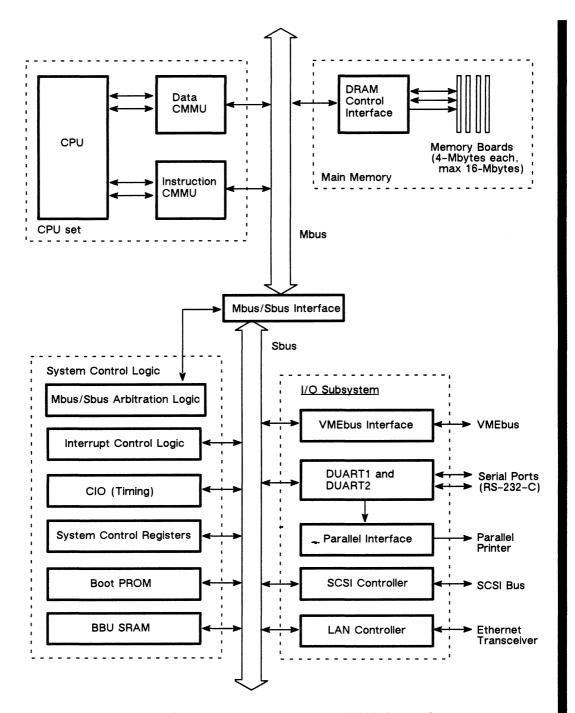

| 1-1                                                                                            | System Board Architecture - 3000 Series 1-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

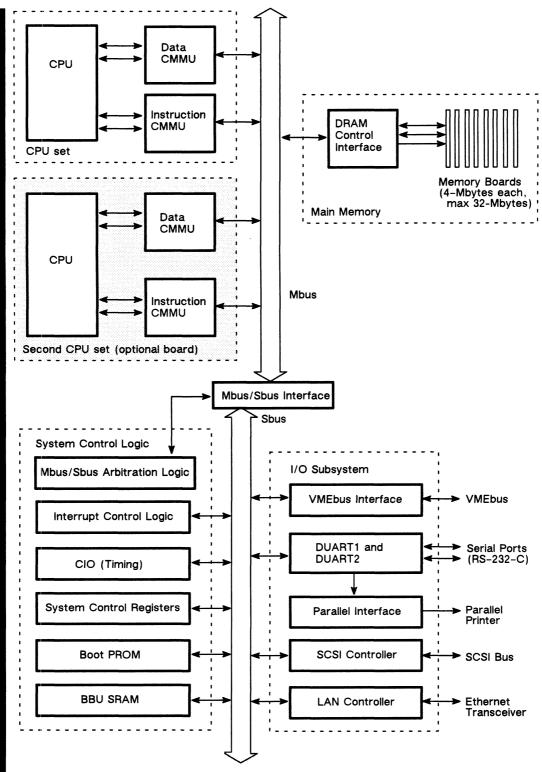

| 1-2                                                                                            | System Board Architecture - 4000 Series 1-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1-3                                                                                            | CPU Set and Main Memory 1-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1-4                                                                                            | Mbus Snooping and Cache Coherency 1-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1-5                                                                                            | CMMU Data Block 1-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

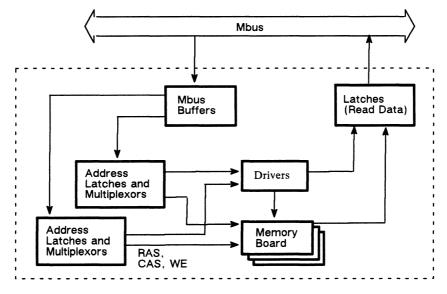

| 1-6                                                                                            | Main Memory 1-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1-7                                                                                            | System Control Logic 1-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

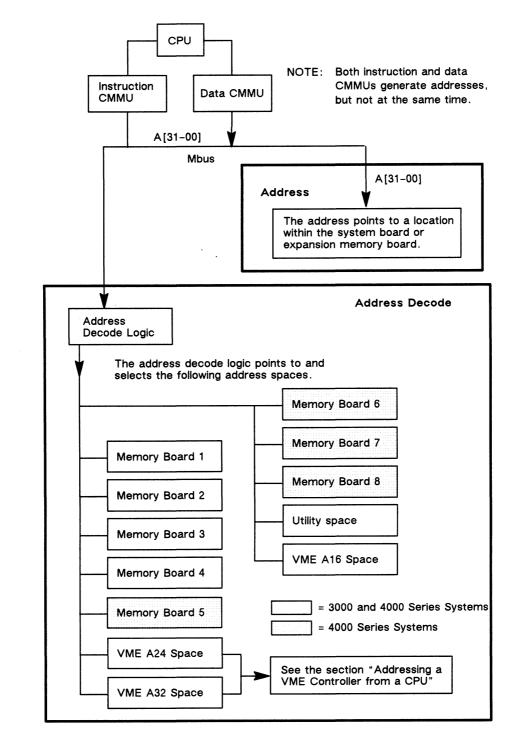

| 1-8                                                                                            | Address Decoding 1-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1–9                                                                                            | VMEbus Grant Daisy-Chain 1-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2-1                                                                                            | Big-Endian Byte Ordering 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

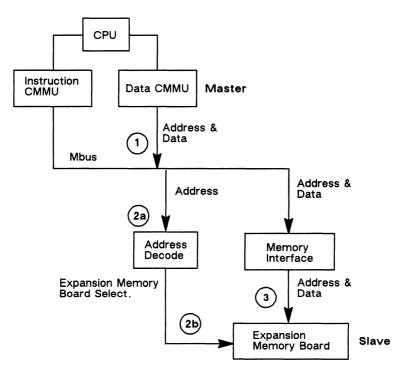

| 2-2                                                                                            | How the CPU Addresses System Memory 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2-3                                                                                            | Decoding Addresses from the CPU 2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 2-4                                                                                            | Addressing the VMEbus from the CPU 2-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2-5                                                                                            | Decoding Addresses to the VMEbus 2-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2-6                                                                                            | Structure of Addresses from VME Controllers to System Memory 2-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2–7                                                                                            | How a VME Controller Addresses System Board Resources and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <b>n</b> 0                                                                                     | System Memory (Flowchart)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2-8                                                                                            | System Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2 0                                                                                            | External Timer Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 2-9                                                                                            | External Timer Connections 2-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3-1                                                                                            | Handling Interrupts with a Single-CPU System Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3-1<br>3-2                                                                                     | Handling Interrupts with a Single-CPU System Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                | Handling Interrupts with a Dual-CPU System Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3-2                                                                                            | Handling Interrupts with a Dual-CPU System Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3–2<br>3–3                                                                                     | Handling Interrupts with a Dual-CPU System Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3-2<br>3-3<br>3-4                                                                              | Handling Interrupts with a Dual-CPU System Board3-5VME Interrupts to the System Board3-23VME Controller Initiating a Level-1 Interrupt to System Board3-24VMEbus Grant Daisy-Chain3-25                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3-2<br>3-3<br>3-4<br>3-5                                                                       | Handling Interrupts with a Dual-CPU System Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 3-2<br>3-3<br>3-4<br>3-5<br>4-1                                                                | Handling Interrupts with a Dual-CPU System Board3-5VME Interrupts to the System Board3-23VME Controller Initiating a Level-1 Interrupt to System Board3-24VMEbus Grant Daisy-Chain3-25The Monochrome Graphics Subsystem4-3                                                                                                                                                                                                                                                                                                                                                                     |

| 3-2<br>3-3<br>3-4<br>3-5<br>4-1<br>4-2                                                         | Handling Interrupts with a Dual-CPU System Board3-5VME Interrupts to the System Board3-23VME Controller Initiating a Level-1 Interrupt to System Board3-24VMEbus Grant Daisy-Chain3-25The Monochrome Graphics Subsystem4-3Monochrome Graphics Video Memory Coordinate System4-12                                                                                                                                                                                                                                                                                                               |

| 3-2<br>3-3<br>3-4<br>3-5<br>4-1<br>4-2<br>4-3                                                  | Handling Interrupts with a Dual-CPU System Board3-5VME Interrupts to the System Board3-23VME Controller Initiating a Level-1 Interrupt to System Board3-24VMEbus Grant Daisy-Chain3-25The Monochrome Graphics Subsystem4-3Monochrome Graphics Video Memory Coordinate System4-12Frame Buffer Organization4-18                                                                                                                                                                                                                                                                                  |

| 3-2<br>3-3<br>3-4<br>3-5<br>4-1<br>4-2<br>4-3<br>5-1                                           | Handling Interrupts with a Dual-CPU System Board3-5VME Interrupts to the System Board3-23VME Controller Initiating a Level-1 Interrupt to System Board3-24VMEbus Grant Daisy-Chain3-25The Monochrome Graphics Subsystem4-3Monochrome Graphics Video Memory Coordinate System4-12Frame Buffer Organization4-18Color Graphics Subsystem (8-Bit)5-2                                                                                                                                                                                                                                               |

| 3-2<br>3-3<br>3-4<br>3-5<br>4-1<br>4-2<br>4-3<br>5-1<br>5-2                                    | Handling Interrupts with a Dual-CPU System Board3-5VME Interrupts to the System Board3-23VME Controller Initiating a Level-1 Interrupt to System Board3-24VMEbus Grant Daisy-Chain3-25The Monochrome Graphics Subsystem4-3Monochrome Graphics Video Memory Coordinate System4-12Frame Buffer Organization4-18Color Graphics Subsystem (8-Bit)5-2Color Graphics Subsystem (24-Bit)5-3Broadcast Data Transfers of 8-bit Registers with 24-bit Color5-10Graphics Subsystem Registers5-14                                                                                                          |

| 3-2<br>3-3<br>3-4<br>3-5<br>4-1<br>4-2<br>4-3<br>5-1<br>5-2<br>5-3                             | Handling Interrupts with a Dual-CPU System Board3-5VME Interrupts to the System Board3-23VME Controller Initiating a Level-1 Interrupt to System Board3-24VMEbus Grant Daisy-Chain3-25The Monochrome Graphics Subsystem4-3Monochrome Graphics Video Memory Coordinate System4-12Frame Buffer Organization4-18Color Graphics Subsystem (8-Bit)5-2Color Graphics Subsystem (24-Bit)5-3Broadcast Data Transfers of 8-bit Registers with 24-bit Color5-10                                                                                                                                          |

| 3-2<br>3-3<br>3-4<br>3-5<br>4-1<br>4-2<br>4-3<br>5-1<br>5-2<br>5-3<br>5-4                      | Handling Interrupts with a Dual-CPU System Board3-5VME Interrupts to the System Board3-23VME Controller Initiating a Level-1 Interrupt to System Board3-24VMEbus Grant Daisy-Chain3-25The Monochrome Graphics Subsystem4-3Monochrome Graphics Video Memory Coordinate System4-12Frame Buffer Organization4-18Color Graphics Subsystem (8-Bit)5-2Color Graphics Subsystem (24-Bit)5-3Broadcast Data Transfers of 8-bit Registers with 24-bit Color5-10Graphics Subsystem Registers5-14                                                                                                          |

| 3-2<br>3-3<br>3-4<br>3-5<br>4-1<br>4-2<br>4-3<br>5-1<br>5-2<br>5-3<br>5-4<br>5-5               | Handling Interrupts with a Dual-CPU System Board3-5VME Interrupts to the System Board3-23VME Controller Initiating a Level-1 Interrupt to System Board3-24VMEbus Grant Daisy-Chain3-25The Monochrome Graphics Subsystem4-3Monochrome Graphics Video Memory Coordinate System4-12Frame Buffer Organization4-18Color Graphics Subsystem (8-Bit)5-2Color Graphics Subsystem (24-Bit)5-3Broadcast Data Transfers of 8-bit Registers with 24-bit Color5-10Graphics Subsystem Registers5-14Global Elements of the POLY Command5-42                                                                   |

| 3-2<br>3-3<br>3-4<br>3-5<br>4-1<br>4-2<br>4-3<br>5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6        | Handling Interrupts with a Dual-CPU System Board3-5VME Interrupts to the System Board3-23VME Controller Initiating a Level-1 Interrupt to System Board3-24VMEbus Grant Daisy-Chain3-25The Monochrome Graphics Subsystem4-3Monochrome Graphics Video Memory Coordinate System4-12Frame Buffer Organization4-18Color Graphics Subsystem (8-Bit)5-2Color Graphics Subsystem (24-Bit)5-3Broadcast Data Transfers of 8-bit Registers with 24-bit Color5-10Graphics Subsystem Registers5-14Global Elements of the POLY Command5-43Z-Buffer Gate Array Components5-72Keyboard Interface Components6-2 |

| 3-2<br>3-3<br>3-4<br>3-5<br>4-1<br>4-2<br>4-3<br>5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7 | Handling Interrupts with a Dual-CPU System Board3-5VME Interrupts to the System Board3-23VME Controller Initiating a Level-1 Interrupt to System Board3-24VMEbus Grant Daisy-Chain3-25The Monochrome Graphics Subsystem4-3Monochrome Graphics Video Memory Coordinate System4-12Frame Buffer Organization4-18Color Graphics Subsystem (8-Bit)5-2Color Graphics Subsystem (24-Bit)5-3Broadcast Data Transfers of 8-bit Registers with 24-bit Color5-10Graphics Subsystem Registers5-14Global Elements of the POLY Command5-43Z-Buffer Gate Array Components5-72                                 |

| 3-2 3-3 3-4 3-5 4-1 4-2 4-3 5-1 5-2 5-3 5-4 5-5 5-6 5-7 6-1                                    | Handling Interrupts with a Dual-CPU System Board3-5VME Interrupts to the System Board3-23VME Controller Initiating a Level-1 Interrupt to System Board3-24VMEbus Grant Daisy-Chain3-25The Monochrome Graphics Subsystem4-3Monochrome Graphics Video Memory Coordinate System4-12Frame Buffer Organization4-18Color Graphics Subsystem (8-Bit)5-2Color Graphics Subsystem (24-Bit)5-3Broadcast Data Transfers of 8-bit Registers with 24-bit Color5-10Graphics Subsystem Registers5-14Global Elements of the POLY Command5-43Z-Buffer Gate Array Components5-72Keyboard Interface Components6-2 |

| 7-1        | 3000 and 4000 Series Serial and Parallel Ports                     |

|------------|--------------------------------------------------------------------|

| 7-2        | 400 Series Serial and Parallel Ports                               |

| 7-3        | Data Strobe Timing for a Data Products Interface                   |

| 7-4        | Data Strobe Timing for a Centronics Interface                      |

| 8-1        | Components of the LAN Interface                                    |

| 8-2        | Sbus Addresses Produced by the LAN Interface                       |

| 8-3        | Conceptual CMMU Page Descriptor Produced by the LAN Interface 8-14 |

| 9-1        | SCSI Port Components                                               |

|            | Initial Power-Up FlowchartB-1                                      |

|            | Reset Flowchart                                                    |

| B-3        | Initialize Flowchart                                               |

| B-4        | PROM-Resident Testing Flowchart                                    |

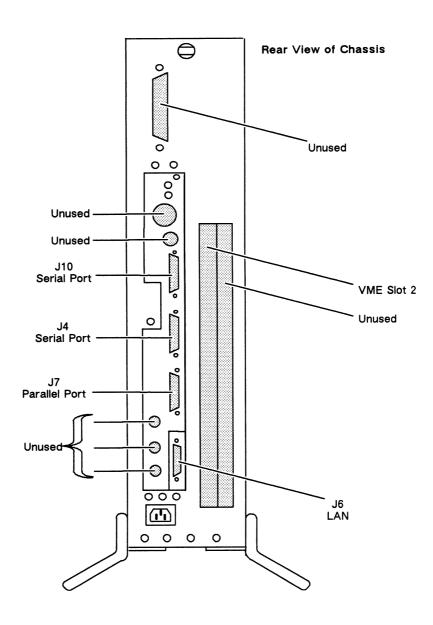

| <b>D-1</b> | 3000 Series External Connectors D-2                                |

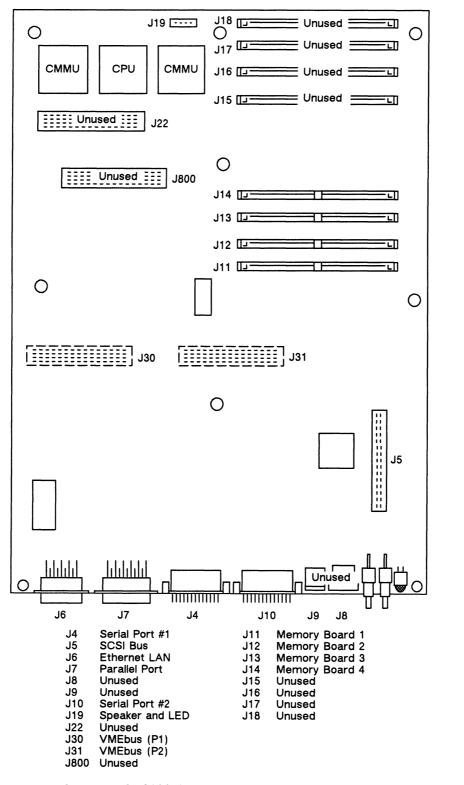

| D-2        | 3000 Series System Board Connectors D-3                            |

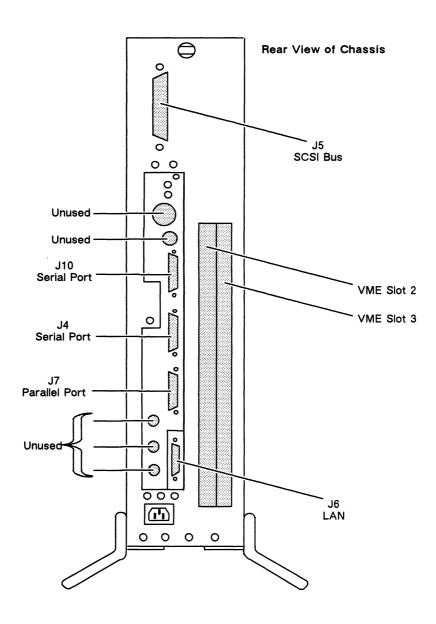

| D-3        | 4000 Series External Connectors D-4                                |

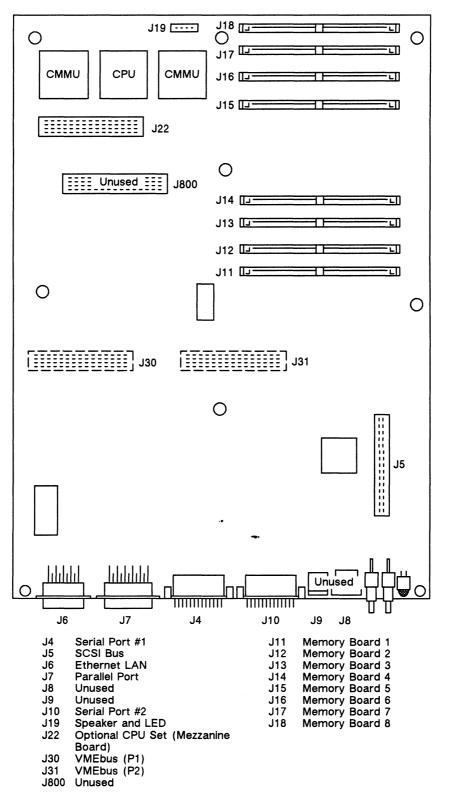

| D-4        | 4000 Series System Board Connectors D-5                            |

| D-5        | 3000 Series VMEbus Connectors D-12                                 |

# Chapter 1 System Board Architecture

This chapter describes the system board architecture, including the following topics:

- System architecture and configuration.

- System board architecture and configuration.

- The CPU set, including the CPU and CMMUs and cache coherency.

- Main memory and the memory interface.

- The Mbus and Sbus, and the interface between them.

- The graphics subsystem, including monochrome graphics, color graphics and the Z-buffer controller (400 series only).

- The I/O subsystem, including the keyboard port, serial ports, parallel port, Ethernet LAN interface, SCSI interface, and VMEbus interface (400 series only). The VMEbus section discusses VMEbus arbitration and VMEbus data transfers.

- Timers available to system programmers.

- Interrupts and the interrupt control logic.

# Architecture and Configuration

Data General's AViiON<sup>™</sup> 3000 and 4000 series systems use the Motorola 32-bit MC88100 RISC (Reduced Instruction Set Computing) processor and the Motorola MC88200 CMMU (Cache/Memory Management Unit). They run either Data General's DG/UX<sup>™</sup> operating system or industry-available operating systems for MC88000-based systems. Figure 1-1 and Figure 1-2 illustrate the system board architecture.

Using 4-Mbyte memory modules, 3000 series systems support 16 Mbytes maximum and 4000 series systems support 32 Mbytes maximum.

Both 3000 and 4000 series systems have internal disk and tape storage which is made possible through a SCSI interface. In addition for 4000 series systems, a compact, free-standing, mass-storage subsystem is available for additional disk or tape storage.

3000 and 4000 series systems do not support graphics.

Table 1-1 summarizes the configurations for 3000 and 4000 series systems.

| ltem                                        | 3000 Series   | 4000 Series |

|---------------------------------------------|---------------|-------------|

| CPU set (1 CPU, 2 CMMUs)                    | 1             | 1 or 2      |

| CPU clock speed (Mhz)                       | 16.67         | 16.67 or 20 |

| DRAM (4-Mbyte modules)                      | 4 - 16 Mbytes | 4 - 32      |

| Mbytes                                      |               |             |

| VMEbus interface                            | 1 slot        | 2 slots     |

| Integrated I/O                              |               |             |

| Parallel port (Centronics or Data Products) | 1             | 1           |

| Serial ports (RS-232-C)                     | 2             | 2           |

| SCSI ports                                  | 1             | 1           |

| SCSI connectors - internal                  | 4             | 4           |

| SCSI connectors – external                  | 0             | 1           |

| LAN interface                               | 1             | 1           |

#### Table 1-1 System Configurations

Figure 1–1 System Board Architecture – 3000 Series Systems

Figure 1-2 System Board Architecture - 4000 Series Systems

# Memory

The memory system consists of main memory, which includes onboard dynamic random-access-memory (DRAM), expansion DRAM boards and the associated memory interface logic, plus static RAM (SRAM) and programmable read-only-memory (PROM).

#### Main Memory

Main memory consists of dynamic random-access-memory (DRAM) and the memory interface logic needed to control accesses to the DRAM (see NO TAG). DRAM memory consists of 4-Mbyte memory modules that plug into the system board. Each 4-Mbyte memory module has 36 1-Mbit, fast-page 100-ns DRAMs that provide 32 data bits and 4 parity bits for each address.

3000 series systems accept as many as four memory modules, for a maximum of 16 Mbytes of RAM. The memory modules plug into the system board.

4000 series systems accept as many as eight memory modules, for a maximum of 32 Mbytes of RAM. The memory modules plug into the system board.

Main memory is contiguous and begins at address 0000 0000. Each location has 36 bits: 32 bits for the data word and 4 bits for parity. The parity logic, located on the system board, generates and checks the parity bits.

The DRAM uses byte parity; one parity bit for each byte of data. The parity bits have separate data-in and data-out connections to the DRAMs, and the write parity data is driven to the DRAMs in a way that allows diagnostic software to force parity bits high during a write to memory. This logic also provides the control signals for refreshing the DRAM array.

Figure 1–6 Main Memory

### **Main-Memory Interface**

The memory interface connects the DRAM to the Mbus, controlling data transfers to and from the DRAM. When a device addresses memory, the memory interface enables the memory module that contains the addressed location; then reads from or writes to the location. The interface consists of the following:

- Address and data latches.

- Address and data drivers.

- Control logic and memory timing to regulate the memory strobes (RAS and CAS) and write enable (WE).

The memory interface responds only to addresses in the lower 128 Mbytes of system address space. Table 1-3 shows the number of clock cycles it takes to execute reads and writes.

|                       | Number of Clock Cycles<br>at CPU Speed: |          |  |  |  |  |  |

|-----------------------|-----------------------------------------|----------|--|--|--|--|--|

| Type of Access        | 16.67 (MHz)                             | 20 (MHz) |  |  |  |  |  |

| Single-word write     | 5                                       | 6        |  |  |  |  |  |

| Single-word read      | 6                                       | 7        |  |  |  |  |  |

| Block write (4 words) | 11                                      | 12       |  |  |  |  |  |

| Block read (4 words)  | 12                                      | 13       |  |  |  |  |  |

Table 1-3 Memory Read and Write Cycles

The memory interface sends status signals to the workstation's Parity Address Register (PAR) to indicate when one or more modules has 100 ns DRAMs installed and the number of modules with 4-Mbit DRAMs. For information on these status bits, see the description of the Parity Address Register (PAR) later in this chapter.

# Battery Backed Up (BBU) SRAM and PROM

The BBU SRAM provides 2 Kbytes of nonvolatile storage for diagnostics, system configuration, and boot information. (Note that within this manual we also refer to the BBU SRAM as NOVRAM or nonvolatile RAM.) The 128-Kbyte PROM contains powerup diagnostic and initialization code, including the local code for booting the system over an Ethernet. The diagnostic registers provide information that allow diagnostic software to control the state of the system board, determine system board status, and obtain Mbus parity error status information.

# Addressing System Board Resources and System Memory

This section describes how to address the system board resources and system memory. The following numbered steps, in conjunction with Figure 2-2 and Figure 2-3, describe how the CPUs access the system board resources and the system memory.

- 1. The CPU puts a 32-bit address onto the Mbus.

- 2. The address decode logic decodes the address bits (2a) and enables access to a device (2b) such as onboard memory, expansion memory boards, utility space, and VME space.

- 3. The 32-bit address points to a location within the selected device.

Figure 2-2 shows how the CPU addresses memory, while Figure 2-3 shows how addresses are decoded.

Figure 2–2 How the CPU Addresses System Memory

Figure 2–3 Decoding Addresses from the CPU

### EXTAD

# **Extended Address**

#### Address FFF8 8010

#### Write only

The extended address register provides the upper eight Mbus address bits when an A24 VMEbus device accesses the Mbus. EXTAD is loaded during powerup with a base address for VME access to system memory.

EXTAD is not affected by either system reset or local reset.

| Bit | Mnemonic   | Function                                                                                                            |

|-----|------------|---------------------------------------------------------------------------------------------------------------------|

| 7-0 | EXT[31-24] | Extended Address.<br>Supplies the address bits A[31-24] to the Mbus when an A24<br>VMEbus device accesses the Mbus. |

# **Programming the System Control Registers**

The system control registers are memory-mapped and are accessed as 32-bit registers. To access a system control register declare it as type int in a C program, or use the Load Register from Memory (ld) or Store Register to Memory (st) instruction in an assembly language program. Table 2-5 identifies the system control registers and their addresses. The rest of this section describes the diagnostic registers.

| Address (hexadecimal) | Туре                                |  |  |

|-----------------------|-------------------------------------|--|--|

| FFF8 40C0             | Write-only                          |  |  |

| FFF8 40C4             | Read-only                           |  |  |

| FFF8 40C8             | Read-only                           |  |  |

| FFF8 8018             | Read-only                           |  |  |

|                       | FFF8 40C0<br>FFF8 40C4<br>FFF8 40C8 |  |  |

| Table 2–5 Memory Map of the System Control | ol Registers |

|--------------------------------------------|--------------|

|--------------------------------------------|--------------|

# Chapter 3 Interrupts, System Errors, and Bus Faults

This chapter discusses the following topics:

- Types of interrupts.

- How the interrupting devices interrupt the CPU.

- How the CPU handles the interrupts.

The workstation has two error reporting mechanisms: bus faults and interrupts. The CMMUs inform the CPU of bus faults, and the interrupt control logic informs the CPU of interrupts generated by the various subsystems.

Interrupts are a means for various system resources (memory, I/O controllers, power supply, etc.) to notify the CPU of a condition that needs attention. Each interrupt has an associated interrupt service routine that the CPU executes. Some interrupts represent a specific interrupt condition (condition-specific interrupts), while others represent one of many possible interrupt conditions (multiple-use interrupts). For specific interrupts, the operating system developer may use a table to associate an interrupt vector with the interrupt. For the multiple-use interrupts, the interrupting device must supply an interrupt vector to the system board CPU.

Interrupt control logic provides the CPU with interrupt information. When devices assert their interrupt request, the interrupt control logic first performs a logical AND of the interrupt requests with the contents of the interrupt mask register; then it asserts the interrupt line (INT) to the CPU. Workstations with two CPUs have two interrupt lines (INT0 and INT1), one for each CPU. In these systems, the interrupt control logic asserts the appropriate line or lines, depending on the masks.

The interrupt service routine reads the interrupt status register (ISR or IST) and if necessary the interrupt enable registers (IENn); then it isolates the interrupt(s).

The device faults for the I/O subsystems are discussed in the related chapters as follows:

Chapter 6 "Programming the Keyboard Interface and Speaker"

Chapter 7 "Programming the Serial Ports and Parallel Port"

- Chapter 8 "Programming the Local Area Network Interface"

- Chapter 9 "Programming the Small Computer System Interface"

# **Types of Interrupts**

Interrupts fall into one of two categories: condition-specific interrupts and multiple-use interrupts.

### **Condition-Specific Interrupts**

Condition-specific interrupts span much of the system, including all of the local system board interrupts and many VME interrupts. These interrupts represent specific conditions such as the depressing of the abort switch or the occurrence of a single-bit memory read error.

#### 3000 and 4000 Series Interrupts

The condition-specific interrupts include Abort Pushbutton (ABT), AC Failure (ACF), Bus Arbitration Timeout (ATO), Parity Error (PAR), CIO Interrupt (CIO), System Failure (SF), Parallel Port Interrupt (PPI), DUART1 Interrupt (DT1), DUART2 Interrupt (DT2), Ethernet Controller Interrupt (ECI), DMA Terminal Count (DTC), DMA Write Protect Error (DWP), DMA Valid Bit (DVB), and SCSI Controller Interrupt (SCI). Of these, the DUART Interrupts (DI1 and DI2) and the CIO Interrupt (CIO) may be one of several possible, but specifically defined, interrupts from the related device.

### Multiple-Use Interrupts (3000 and 4000 Series)

Multiple-use interrupts include Signal High Priority (SHP), Signal Low Priority (SLP), Software-Generated Interrupts (SI[7-0]), and VME Interrupts (IR[7-1]). VME interrupts are generated by VME controllers through seven interrupt request lines (IRQ[7-1]\*) on the VMEbus. A VME controller can choose which interrupt line to use when it has an interrupt condition that requires servicing by the system board. These interrupt lines are not limited to specific interrupts; any serviceable interrupt can be generated through the VME interrupt request lines. To execute the correct interrupt service routine, the system board CPU must obtain the interrupt vector from the interrupting VME controller.

Besides being interrupted, the system board CPU can initiate interrupts to the VME controllers using the VME-level interrupts. The CPU, when it interrupts a VME controller, must define the interrupt level and provide the VME controller with an interrupt vector. This process is described later in this chapter in the section "Interrupting a VME Controller."

## SWIR (300 Series Only)

## Software Interrupt

#### Address FFF8 4014

#### Write Only

The Software Interrupt Register (SWIR) initiates software interrupts.

The SWIR bits are defined as follows:

| Bit | Name     | Function                                                                                                                                                                                                                                                                             |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-1 | Reserved | Ignore these bits.                                                                                                                                                                                                                                                                   |

| 0   | SWI      | <ul> <li>Software interrupt.</li> <li>1 Interrupts the CPU. The status of this bit is reflected by ISR bit 9 (SI). Writing a 0 to IER bit 9 masks this interrupt.</li> <li>0 Clears the interrupt request. This bit is not set to 0 after system reset or power-on reset.</li> </ul> |

Even though a reset does not enable the software interrupt request, software must ensure that bit 0 of the SWIR is set to 0 before enabling the interrupt after a reset.

### 3000 and 4000 Series CPU Interrupt Registers

This section describes the registers used to interrupt the CPU in 3000 and 4000 series systems.

IEN0, IEN1 (3000 and 4000 Series Only)Interrupt EnableIEN0Address FFF8 4004WriteIEN1Address FFF8 4008WriteThe Interrupt Enable registers (IEN0 and IEN1) enable and mask interrupts to the

CPUs. IEN0 and IEN1 enable interrupts to CPU0 and CPU1, respectively (a single-processor system uses only IEN0). To enable an interrupt, write a 1 into the corresponding bit in IEN0 or IEN1. To mask an interrupt, write a 0 into the corresponding bit in IEN0 or IEN1. The bits in the IST register and the Interrupt Enable registers are mirror images of each other. A system reset clears all Interrupt Enable register bits to 0; a local reset does not affect these registers.

The following bitbox and bit descriptions delete the Z-buffer (ZBF), Video (VDI), and keyboard (KBD) interrupts.

| 31  | 30  | 29  | 28   | 27   | 26       | 25       | 24  | 23  | 22       | 21  | 20 | 19  | 18  | 17  | 16  |

|-----|-----|-----|------|------|----------|----------|-----|-----|----------|-----|----|-----|-----|-----|-----|

| ABT | ACF | АТО | Rese | rved | Reserved | Reserved | PAR | IR7 | Reserved | CIO | SF | IR6 | PPI | DI1 | DI2 |

|   | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 87       | 6   | 5   | 4   | 3    | 2    | 1   | 0   |

|---|-----|-----|-----|-----|-----|-----|-----|----------|-----|-----|-----|------|------|-----|-----|

| ſ | ECI | IR5 | DTC | IR4 | DWF | IR3 | DVB | Reserved | IR2 | SCI | IR1 | Rese | rved | SI1 | S10 |

| Bit    | Name     | Function                                                                                                                        |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------------|

| 31     | ABT      | Abort.<br>1 Enables the abort pushbutton interrupt.<br>0 Masks the abort pushbutton interrupt.                                  |

| 30     | ACF      | Ac failure.<br>1 Enables the ac power failure interrupt.<br>0 Masks the ac power failure interrupt.                             |

| 29     | ΑΤΟ      | <ul><li>VMEbus timeout.</li><li>1 Enables the VMEbus timeout interrupt.</li><li>0 Masks the VMEbus timeout interrupt.</li></ul> |

| 28, 27 | Reserved | Write a 0 to these bits.                                                                                                        |

| 26     | Reserved | Was Zbuffer interrupt                                                                                                           |

| 25     | Reserved | Was Video interrupt                                                                                                             |

|        |          |                                                                                                                                 |

(continued)

| 24 |          |                                                                                                                                                                |

|----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | PAR      | Parity error.<br>1 Enables the parity error interrupt.<br>0 Masks the parity error interrupt.                                                                  |

| 23 | IR7      | <ul><li>VMEbus level 7.</li><li>1 Enables the level 7 interrupt from the VMEbus.</li><li>0 Masks the level 7 interrupt from the VMEbus.</li></ul>              |

| 22 | Reserved | Was Keyboard interrupt                                                                                                                                         |

| 21 | CIO      | CIO.<br>1 Enables the CIO interrupt.<br>0 Masks the CIO interrupt.                                                                                             |

| 20 | SF       | System failure.<br>1 Enables the system failure interrupt.<br>0 Masks the system power failure interrupt.                                                      |

| 19 | IR6      | <ul><li>VMEbus level 6.</li><li>1 Enables the level 6 interrupt from the VMEbus.</li><li>0 Masks the level 6 interrupt from the VMEbus.</li></ul>              |

| 18 | PPI      | Parallel port.<br>1 Enables the parallel port request interrupt.<br>0 Masks the parallel port request interrupt.                                               |

| 17 | DI1      | DUART1.<br>1 Enables the DUART1 interrupt.<br>0 Masks the DUART1 interrupt.                                                                                    |

| 16 | DI2      | DUART2.<br>1 Enables the DUART2 interrupt.<br>0 Masks the DUART2 interrupt.                                                                                    |

| 15 | ECI      | Ethernet controller.<br>1 Enables the Ethernet controller request interrupt.<br>0 Masks the Ethernet controller request interrupt.                             |

| 14 | IR5      | <ul> <li>VMEbus level 5.</li> <li>1 Enables the level 5 interrupt from the VMEbus.</li> <li>0 Masks the level 5 interrupt from the VMEbus.</li> </ul>          |

| 13 | DTC      | <ul> <li>DMA terminal count</li> <li>1 Enables the DMA terminal count interrupt.</li> <li>0 Masks the DMA terminal count interrupt.</li> </ul>                 |

| 12 | IR4      | <ul> <li>VMEbus level 4.</li> <li>1 Enables the level 4 interrupt from the VMEbus.</li> <li>0 Masks the level 4 interrupt from the VMEbus.</li> </ul>          |

| 11 | DWP      | <ul> <li>DMA write protect error.</li> <li>1 Enables the DMA write protect error interrupt.</li> <li>0 Masks the DMA write protect error interrupt.</li> </ul> |

| 10 | IR3      | <ul><li>VMEbus level 3.</li><li>1 Enables the level 3 interrupt from the VMEbus.</li><li>0 Masks the level 3 interrupt from the VMEbus.</li></ul>              |

(continued)

Interrupts

| Bit | Name     | Function                                                                                                                                           |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 9   | DVB      | <ul><li>DMA valid bit.</li><li>1 Enables the DMA valid bit interrupt.</li><li>0 Masks the DMA valid bit interrupt.</li></ul>                       |

| 8,7 | Reserved | Write a 0 to these bits.                                                                                                                           |

| 6   | IR2      | <ul><li>VMEbus level 2.</li><li>1 Enables the level 2 interrupt from the VMEbus.</li><li>0 Masks the level 2 interrupt from the VMEbus.</li></ul>  |

| 5   | SCI      | <ul><li>SCSI controller.</li><li>1 Enables the SCSI controller request interrupt.</li><li>0 Masks the SCSI controller request interrupt.</li></ul> |

| 4   | IR1      | <ul><li>VMEbus level 1.</li><li>1 Enables the level 1 interrupt from the VMEbus.</li><li>0 Masks the level 1 interrupt from the VMEbus.</li></ul>  |

| 3,2 | Reserved | Write a 0 to these bits.                                                                                                                           |

| 1   | SI1      | Software-generated interrupt 1.<br>1 Enables software interrupt 1.<br>0 Masks software interrupt 1.                                                |

| 0   | SI0      | <ul><li>Software-generated interrupt 0.</li><li>1 Enables software interrupt 0.</li><li>0 Masks software interrupt 0.</li></ul>                    |

(concluded)

Read

### IST (3000 and 4000 Series Only)

## Interrupt Status

#### Address FFF8 4040

The Interrupt Status (IST) register contains the current state of all interrupt requests. When a device generates an interrupt, the interrupt logic sets the corresponding bit in the IST register.